Part Number: TCAN4550-Q1

Other Parts Discussed in Thread: TCAN4550

Hi team,

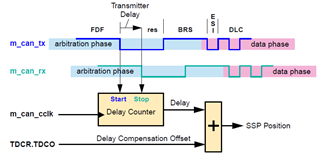

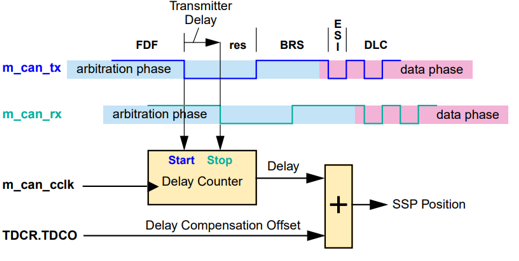

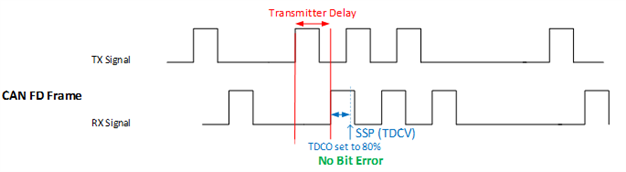

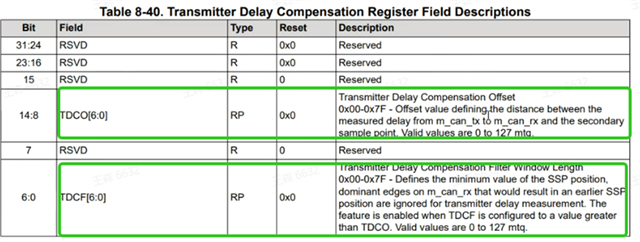

Customer has found some fault frame issue in project and they'd like to adjust the delay compensation register to fix it. Could you help share

1. if any guideline to set below TDCO and TDCF register?

2. how long is mtq?

3. what's the relationship between TDCO, TDCF and TDCV

*Use external 40M crystal oscillator

thank you

Scarlett