Part Number: DS320PR810

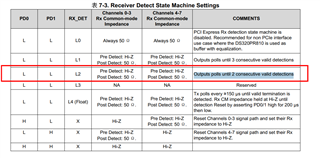

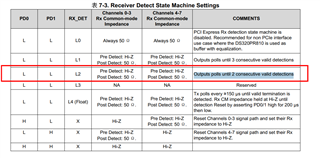

1、Receive state detection configuration, which state are these configurations for?

2、How to understand the content here? How does this slow speed of Gen2.0 finally work?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: DS320PR810

1、Receive state detection configuration, which state are these configurations for?

2、How to understand the content here? How does this slow speed of Gen2.0 finally work?

Hi Aiwen,

1. These configurations are all for PCIe applications. The main difference between all the cases are the amount of detections required before Rx_det is asserted. The other case is for non-PCIe applications where our device is used as a buffer. It's just a matter of how fast you want to detect.

2. I am not following what you're asking here? PCIe links gen3 and up go through a process called link equalization which essentially connects the Root complex (RC) to the endpoint.

Please refer to this appnote on more information regarding link training in PCIe: www.ti.com/.../snla415.pdf

Regards,

Vicente

Hi vicente;

I understand that PCIE3 need link training, but pcie 1.and pcie2.0 don`t need link training, How does this slow speed of Gen2.0 finally work?How exactly is it applied about pcie 1.and pcie2.0 ?

The current problem is that DS320PR180 used on PCIE gen2 will recognize *8 devices as *4 or *2,Why is this the case? What is the solution?

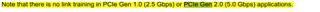

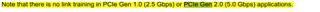

I don`t understand the "Note that there is no link training in PCIe Gen 1.0 (2.5 Gbps) or PCIe Gen 2.0 (5.0 Gbps) applications", If I want to use Gen 1.0 (2.5 Gbps) or PCIe Gen 2.0 (5.0 Gbps), how do I configure it? Do you have a reference design about this?

Hi Aiwen,

PCIe gen1 & 2 loss budget is larger compared to say PCIe gen5 (36db assuming no signal conditioning). Eventually data rates got so fast with the distance needed to transmit being large that the idea of a signal conditioner was introduced.

All newer PCIe devices must be backwards compatible with PCIe gen1.0 & 2.0 by spec. All PCIe links start with gen1 which is the lowest and most fundamental data rate before transitioning to higher data rates.

PCIe 1.0 are 2.0 are 20 and 16 year old specifications. We don't have reference designs for this.

I am not following you issue here. I understand that DS320PR810 is being used. Is the issue it only manages to establish a gen2 link instead of a gen5 link? I also don't understand what you mean by "will recognize 8 devices" please elaborate on this...

Please read pages 5 & 6 of the appnote I attached. It explains how PCIe gen1/2 link training occurs. PCIe Gen3 and above require link equalization but all PCIe links go through link training.

Regards,

Vicente

Hi vicente;

Now the problem we encounter is that when using the DS320's GEN2, the *8-channel device will be recognized as *4 channel or *2 channel,The customer wants to know the application and configuration of the DS320 and DS160 on GEN2, whether there is a complete test, whether the GEN2 rate is really supported, and the application and configuration of the GEN2 is not fully shown in the datasheet。

Hi Aiwen,

It's a small possibility customer might be using incorrect CTLE settings and thus be over equalizing if they're seeing only a gen2 link instead of a gen5 link and thus fall into x8 or x2.

I recommend reducing CTLE and or using a scope to observe eye for anything unusual. This can be done using Tx compliance test if customer has means.

PCIe protocol negotiation always starts with Gen1. Does customer gen into Gen1 full length every time?

I recommend trying different RC and EP if possible to see if the same behavior is seen.

Regards,

Vicente