Part Number: DP83TC812R-Q1

hi

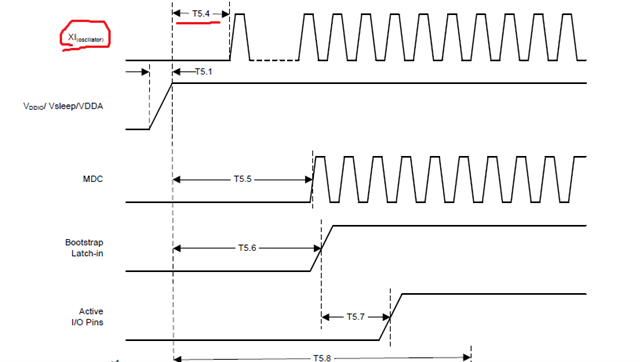

Customer would like to use 812 in RMII slave mode, 50Mhz reference clock is provided by SOC (AM62A). However, it' pretty hard to control the XI timing vs VDDx (T5.4), XI might comes earlier than VDDx or later than T5.4

1. I don't see minimum time of T5.4, is XI ramp earlier than VDD acceptable?

2. If reference clock ramps later than 10ms, does a hard reset help mitigate the risks?

Regards,

Dongbao