Hello, Engineer:

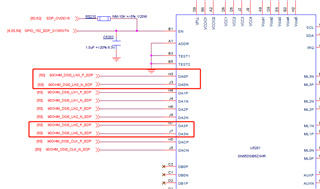

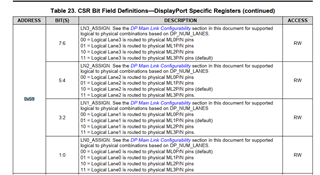

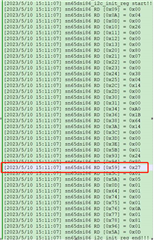

When we use the TI SN65DSI86 chip, the hardware design is reversed with lan0 and lan3 of mipi, so the sequence is reversed. We want to adjust the sequence of lan0 and lan3 through the 0x59 register of the chip, but at present it does not take effect after writing 0x27 to 0x59, the edp screen cannot light up the display, and the IIC communication is normal.

After the hardware is operated on the fly line, the same set of software is used. At this time, the 0x59 register is not written and the screen can be lit up successfully. Therefore, can lan0 and lan3 be adjusted by writing the corresponding value to register 0x59? If so, how should it be adjusted and what values should be written?