Hi Experts,

Good day.

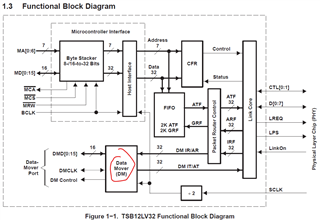

I’m using LLC TSB12LV32 in a new design and during prototype testing we’ve come across the following issue.

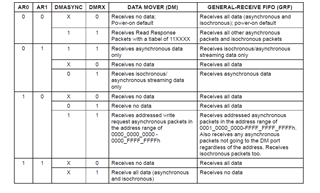

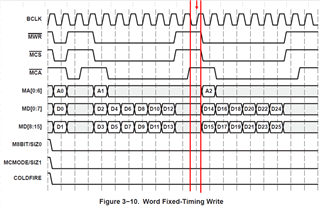

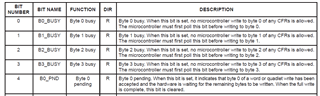

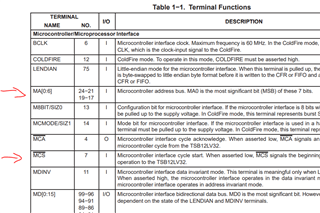

The internal configuration register “Isochronous Port” stays all 0’s when written with a valid “word fixed-timing write” sequence. It is also read by a valid “word fixed-timing read” sequence and shows that the newly written value did not take. The LLC’s MCA pin also acknowledges that the LLC was written or read with a valid set of data. When we perform repeat write/read sequences we notice the value does take after multiple retries. We’ve also noticed that sometimes the upper half or lower half of the word does take in the register while the other half stays 0s. Once the LLC registers are fully set up after multiple retries everything else like data transfer from the MCU to PHY works without any known issues.

- We have it configured for microcontroller interface fixed-timing mode with a 50MHz crystal oscillator.

- We have logic analyzer data that shows proper hold timing from the MCU’s commands to the LLC. We also have o-scope captures that show signal integrity for signals BCLK, MWR, MCS, and MCA being within voltage level and timing tolerance.

- We’ve also checked the reset signal to ensure the IC wasn’t going into reset between a write and read sequence.

We aren’t sure what the issue is given that everything so far checks out with the given datasheet for this IC.

Please advise

Regards,

Josel