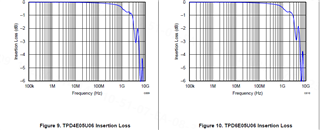

Part Number: TPD6E05U06

Customer feedback that the USB3.0 requirements cannot be met when using this product。

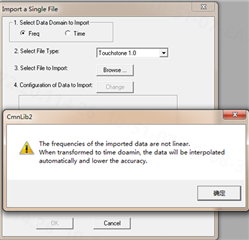

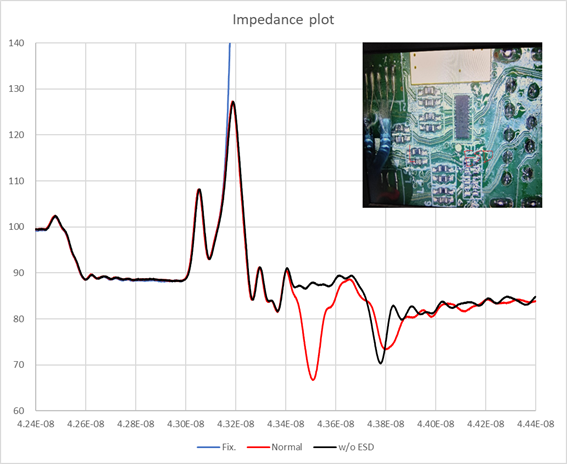

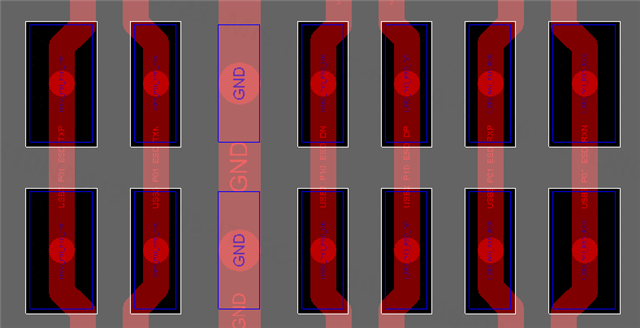

Do we have the related SI mode of high speed test?

Or any other experiment results?

Which could convince customers that this is not our device's problem.