Part Number: SN65DPHY440SS

Hello Expert,

Our customer is evaluatiing and debugging.

Could you please check and give us your opinion?

The part is being used for MIPI signal between Image Sensor and SoC, and the usage specifications are as follows.

-. Interface: MIPI CSI-2 4lane, Datarate: 1.188Gbps, Input Trace: 30cm, Output Trace: 3cm

As for the issue, MIPI signals are not output properly in about 10 out of 40 MAIN BDs manufactured using the part.

The problematic part is the DATA0 line of the part, and the remaining DATA1~3 and CLK are output normally.

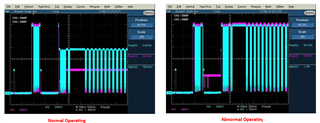

When we checked the signal, the level of the LP signal goes up to 1.2V in B'D where MIPI operates normally.

However, in the abnormally operating B'D, only 0.776V on the INPUT side of Data0 and 0.4V on the OUTPUT side come out.

Therefore, MIPI communication is attempted between the Image Sensor and the SoC, but communication does not seem to be performed properly because the signal level is not matched.

If you need our schematic and top side pcb layout, we can share these.

We would like to be talked privately.

Best Regards,

Michael