Other Parts Discussed in Thread: DS90UB949-Q1, , ALP

Hello,

One customer has below problem used DS90UB948+DS90UB949.

Ds90ub949-q1 is used with DS90UB948-Q1,hdmi output to ds90ub949, 948 output to screen, the screen is not displayed but the backlight of the screen is bright, and i2c can communicate with Ds90ub949-q1 and S90UB948-Q1.

T he pattern test is performed, the screen is also not displayed.

Perform the configuration according to 4.4 Cases in the SNLA132G document. Use the Without FPD-link III scheme and configure 948 to enter Pattern test. The screen displays no information.

code show as below:

{

//1. Set Pixel Clock and Active Frame Size 1920

ds90ub948_single_write(ds90ub948, 0x66, 0x07);

ds90ub948_single_write(ds90ub948, 0x67, 0x80);

ds90ub948_single_write(ds90ub948, 0x66, 0x08);

ds90ub948_single_write(ds90ub948, 0x67, 0x87);

ds90ub948_single_write(ds90ub948, 0x66, 0x09);

ds90ub948_single_write(ds90ub948, 0x67, 0x43);

//2. Set Total Frame Size 2200

ds90ub948_single_write(ds90ub948, 0x66, 0x04);

ds90ub948_single_write(ds90ub948, 0x67, 0x98);

ds90ub948_single_write(ds90ub948, 0x66, 0x05);

ds90ub948_single_write(ds90ub948, 0x67, 0x58);

ds90ub948_single_write(ds90ub948, 0x66, 0x06);

ds90ub948_single_write(ds90ub948, 0x67, 0x46);

//3. Set Back Porch

ds90ub948_single_write(ds90ub948, 0x66, 0x0C);

ds90ub948_single_write(ds90ub948, 0x67, 0x94);

ds90ub948_single_write(ds90ub948, 0x66, 0x0D);

ds90ub948_single_write(ds90ub948, 0x67, 0x24);

//4. Set Sync Width

ds90ub949_single_write(ds90ub948, 0x66, 0x0A);

ds90ub949_single_write(ds90ub948, 0x67, 0x2C);

ds90ub948_single_write(ds90ub948, 0x66, 0x0B);

ds90ub948_single_write(ds90ub948, 0x67, 0x05);

//5.Set Sync Polarities

ds90ub948_single_write(ds90ub948, 0x66, 0x0E);

ds90ub948_single_write(ds90ub948, 0x67, 0x00);

//6.Enable Pattern Generation

ds90ub948_single_write(ds90ub948, 0x65, 0x0C);

ds90ub948_single_write(ds90ub948, 0x64, 0x05);

}

How should I judge the problem?

How to make patgen work only on deserializers before using patgen via FPD-Link?

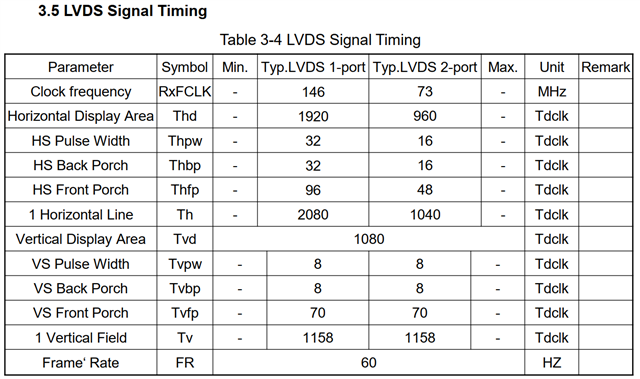

The Display parameter is as following:

Please give me a reply. Thank you very much

Best regards

Kailyn