Hi,

I have a design that uses the MAX3221 interface chip. The design has been stable for a number of years, but has recently started to present problems, which was traced to an increase in noise on our 5V rail when a new batch of MAX3221 chips was used. Swapping the chip back to one with an older date code appeared to reduce the noise and fix the problem.

On a related thread it was mentioned that a die change had happened about a year or so ago MAX3221: MFR differences - Interface forum - Interface - TI E2E support forums. I have a couple of questions:

What did this change do to the switching performance of the switches in the charge pump?

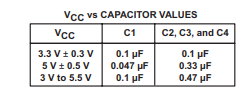

Has TI changed its recommended filtering for the chip? (Note, using the datasheet recommended 100nF cap on Vcc we get more than 700mV pp noise)

Was a PCN issued for this change?

Q.K.