Part Number: TLK10232

Hello

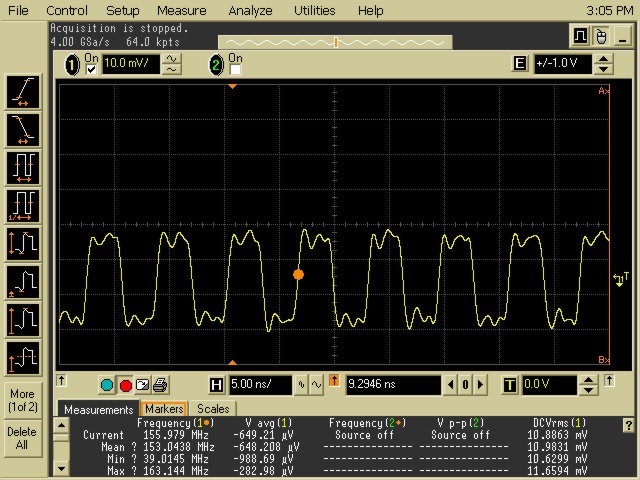

In my TLK10232 design I have noticed something that could be a coincidence or might mean something: When the Refclk input is driven by a steady CO, the phy is working and traffic flows. When Refclk is driven by a clock coming from an FPGA or a DPLL, the phy is not working (there are continuous data errors). I have measured the clock input in all cases, all clocks are fine. The difference is that problems occur when the clock is not present immediately after power-up (both the DPLL and FPGA are configured with a significant delay after power up). However, in all cases, Reset goes up after the clock has been applied. So could the power-up clock delay cause such problems?