Hi,

We are working whit a custom board based on the imx8mp that has the SN65DSI83 used to connect a LVDS display to the SOC. The OS has been generated using Yocto hardknott and the NXP BSP. We are using the kernel version 5.10.72.

The register values we are using are:

Register Value 0x0D 0x00 0x0A 0x05 0x0B 0x10 0x10 0x20 0x12 0x11 0x18 0x78 0x19 0x02 0x1a 0x02 0x20 0xE0 0x21 0x01 0x24 0x10 0x25 0x01 0x28 0x10 0x29 0x00 0x2C 0x04 0x2D 0x00 0x30 0x04 0x31 0x00 0x34 0x2b 0x36 0x0c 0x38 0x08 0x3A 0x08

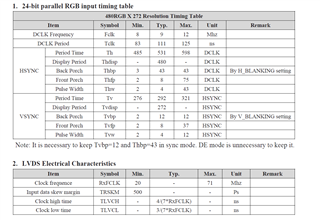

The connected display has 480x272 pixels resolution and the display parameters showed in the datasheet are:

The LVDS clock frequency we measure on the side of the display is 28960000 Hz.

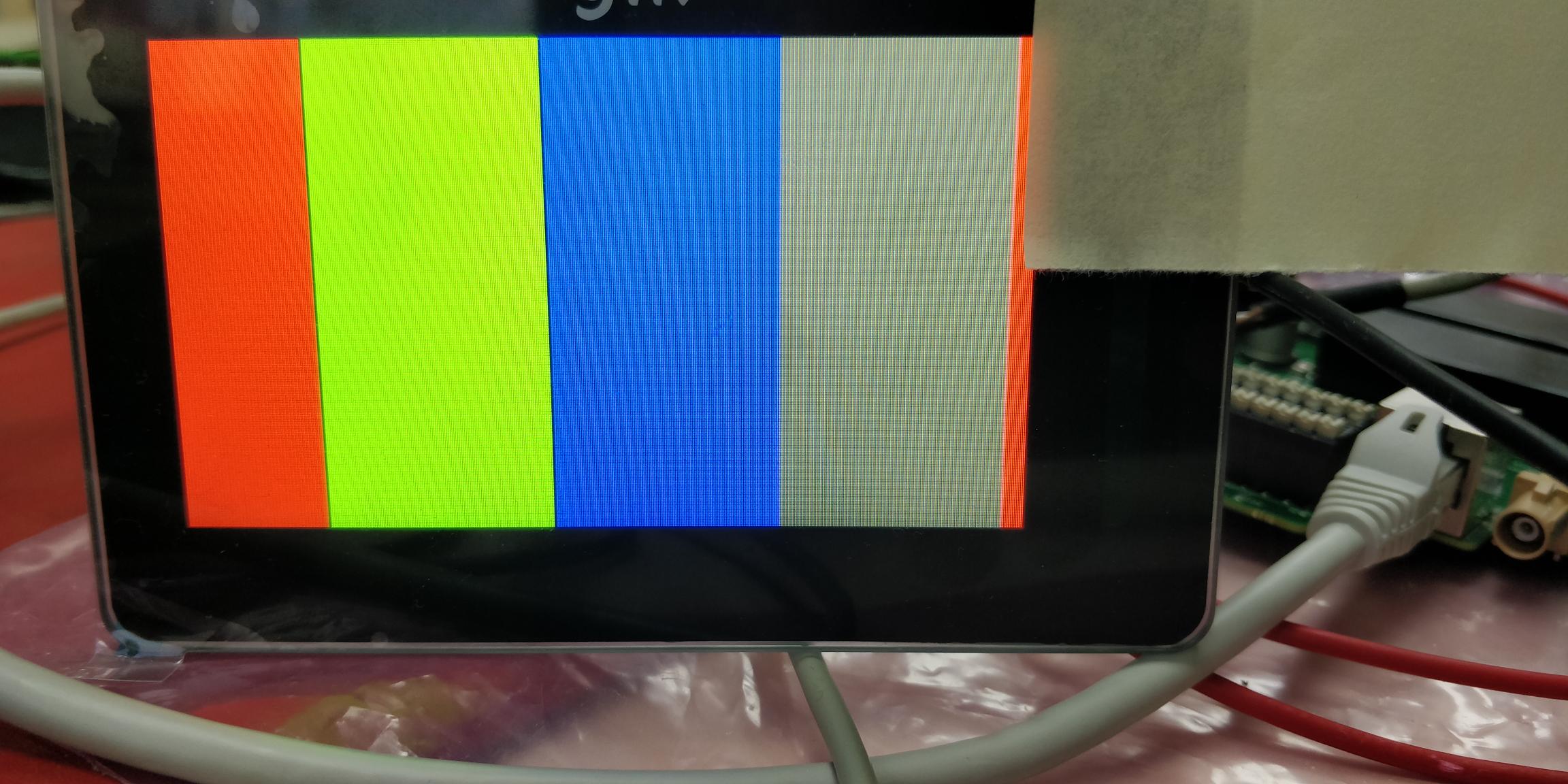

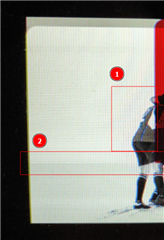

The resulting image is:

In the point 1 the edges should be white but it is painted in blue color.

In the point 2 there this a color change horizontally which is not in he original image.

Is there an incorrect value stored in any of the registers?? What parameters can affect what is shown in points one and two of the image above?

Regards,

Gustavo Plaza.