Part Number: DS90UB948-Q1

Other Parts Discussed in Thread: ALP

Hi team,

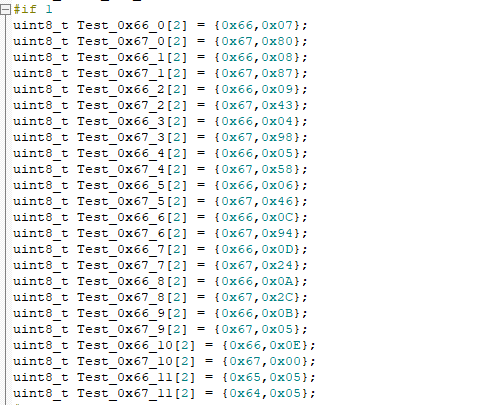

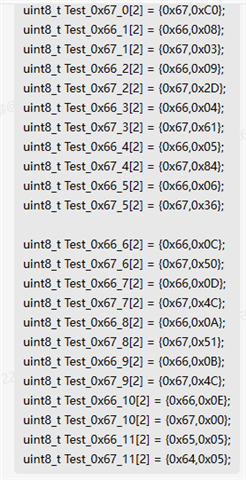

The customer use 948 for splitter mode. And their configuration is as below:

But the second display can't show any image and the first display works normally as below. Could you explain the reason? Or could you tell me how to troubleshoot this problem?