Hello guys.

One of my customers uses TL16C752B for their current products using their stock of the device.

But the stock will be run out in a few months. So they are evaluating TL16C752C for TL16C752B replacing.

In the evaluation. a parity error was happened under following conditions.

Could you please give me your reply or any counter measure?

Q.

We are evaluating TL16C752C on current production board for TL16C752B replacing.

At that time, a parity error was happened when data was received continuously.

Operating conditions are below.

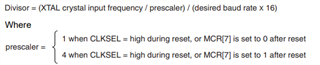

Input clock 19.6608MHz, 4800bps, data 7bit, even parity, stop bit1.

When the internal divisor value for baud rate setting is -1 from the current value,

the parity error was resolved and the sent data from external was received correctly.

Our questions are the follows.

1. Is the countermeasure (decrement 1 from current divisor value) correct?

2. Why was the parity error happened?

3. Was there any similar case in past?

When the baud rate was changed to 9600bps case, the parity error was solved without the countermeasure above.

Your reply would be much appreciated.

Best regards,

Kazuya.