Other Parts Discussed in Thread: , TEST2

Hi team.

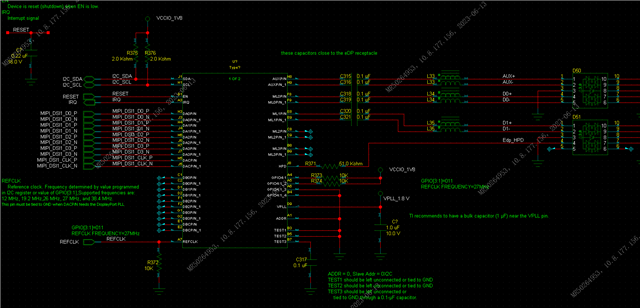

About the REFCLK,

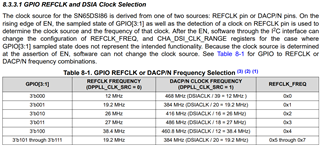

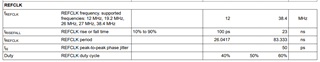

1. this frequency is defined by GPIO[3:1], there are 12 MHz, 19.2 MHz, 26 MHz, 27 MHz, and 38.4 MHz. Optional, how to choose, whether the screen and main control chip corresponding to different frequencies request?

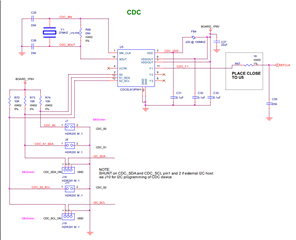

2. This pin is connected to the host control terminal, what are the specific requirements for the pins of the host control terminal? Can any GPIO port meet the requirements?

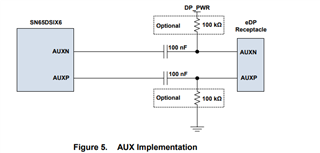

Could you pls help to check the sch? Thanks a lot!

Thanks!

Rayna