Part Number: DP83826E

Other Parts Discussed in Thread: ASH, DP83826I,

Hi,

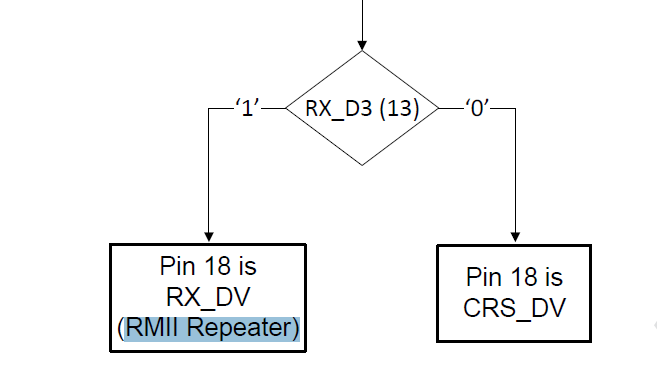

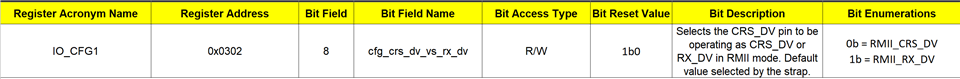

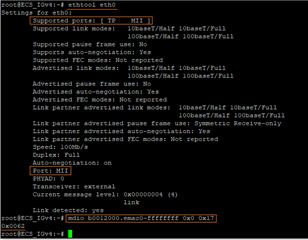

I am looking to configure DP83826E using MDIO interface (from Linux host/mdio-tools), and not strap pins.

I can set speed, auto-negotiate this way by writing to 0x0 (BMCR) register - though can't seem to find how

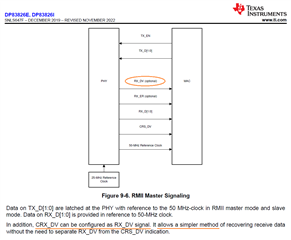

to set "RMII master mode" (without setting Strap4 pin high) in Basic mode? Please advise.

Is there some doc/note that explains where (which register bits) strap pins sampled at reset are recorded?

Thinking perhaps that might shed light on how to bypass strap pins and write config exclusively via MDIO.

Thanks for your timely attention and help.