Part Number: DS90UB948-Q1

Hi,

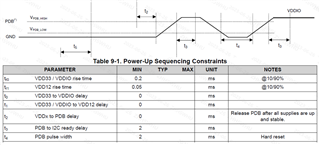

we found that the 948's datasheet has some requirements for PDB pin,( as the below screenshot.)

I want to know how to test t3 & t4.

Now, I will use LOCK pin as indicate is ok or not? because I got a message that PDB pin need reset one time, after LOCK is pull-up ,but i am not sure.

Could you help to confirm that both ( LOCK & PDB ) relation ?

thank you!