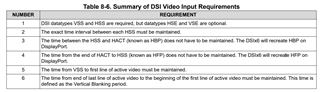

Hi everyone,

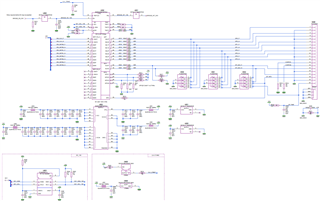

we are using a SN64DSI86 DSI-DP bridge on our board with RZ/V2L with DisplayPort being routed to a DP connector. We have tried it with several different monitors, and we consistently observe the same behavior: 480p works alright, 720p is unstable (blacking out every couple seconds) and 1080p doesn't work at all (black screen). I understand that it could happen if video mode timings are set incorrectly, but I re-checked several times that they are currently correspond to timings taken from EDID of the monitor.

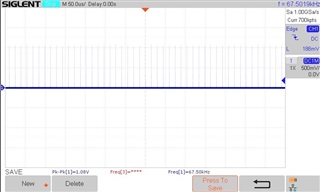

The DP part is stable. I have verified it in a bridge test mode, no issues found in any resolution.

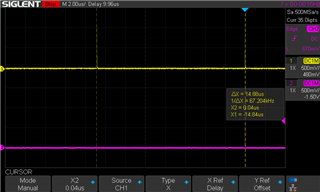

But DSI itself produces this instability. For example, when using 720p mode, within 1s of clearing status registers I observe fail flags: DPTL_UNEXPECTED_HSYNC_ERR, DPTL_UNEXPECTED_PIXEL_DATA_ERR, CHB_SOT_SYNC_ERR, LOSS_OF_DP_SYNC_LOCK_ERR.

It was tested on the latest renesas kernel rz-5.10-cip29-rt12.

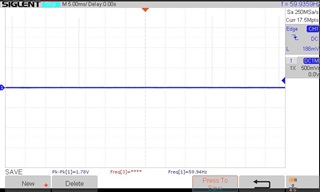

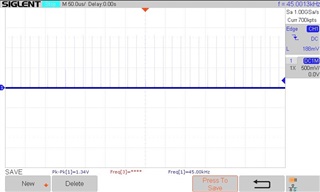

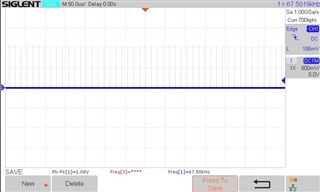

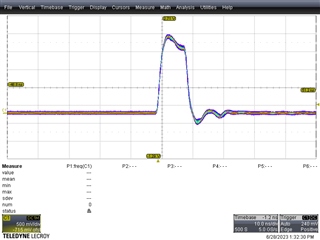

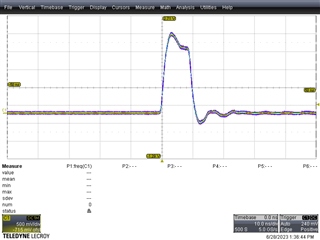

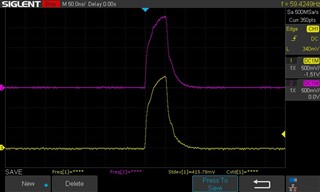

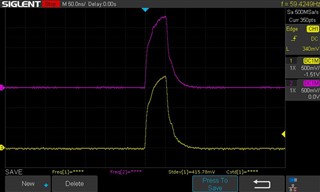

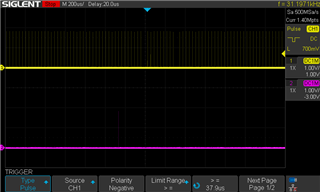

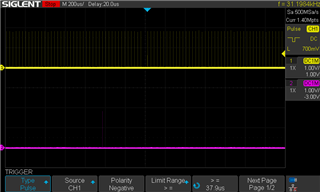

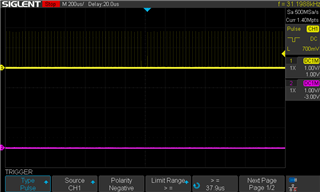

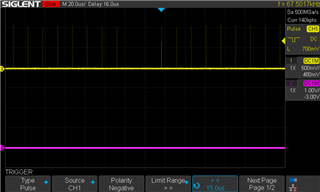

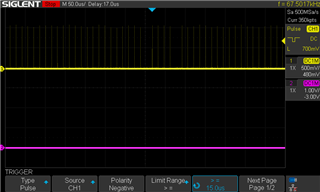

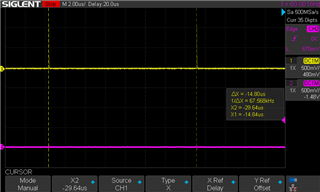

We have also also checked signal integrity and ensured that it is not the issue as well.

What can be the issue? What can I check?