Hi Ti engineer,

I have some problems in the process of using, please help me to see where I made mistakes.

The usage scenario is as follows:

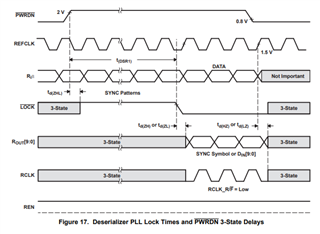

The timing diagram of the 1023a chip is shown in Figure 1

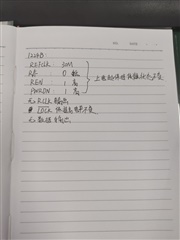

The configuration clock and pin level of the 1224b chip are shown in Figure 2:

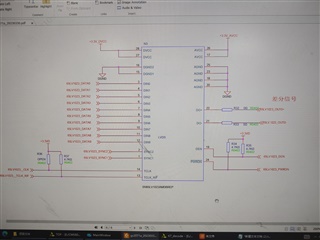

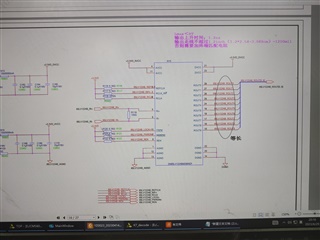

1023a and 1224b Schematic diagram:

1023a and 1224b Schematic diagram:

The questions are as follows:

1. Chip initialization operations mentioned in the manual Do the pwrdn pins of both chips need to be pulled down for a period of time and then pulled up to complete the initialization?

2. Answer question 1, how long will it take to pull down?

3. Connect to question 1. Do you need to perform initialization only once after power-on? Or every 1206 output data needs to perform an initialization operation.

4. My 1224b no clock and data output is missing which step?

5. Please help to see if there is any problem with the chip circuit.