Part Number: DS90UB949A-Q1

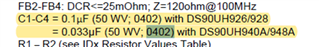

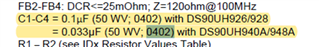

1, 949 C1-C4 note 50WV, 0402, what’s the meaning of 50WV?

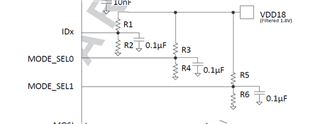

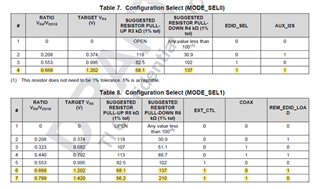

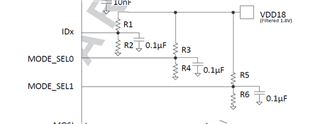

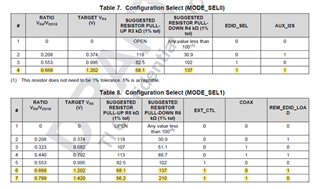

2,configure PIN add 0.1u, when the sampling time? If the up resistor bigger, power up RC will need time.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: DS90UB949A-Q1

1, 949 C1-C4 note 50WV, 0402, what’s the meaning of 50WV?

2,configure PIN add 0.1u, when the sampling time? If the up resistor bigger, power up RC will need time.

Hi Songlin,

1) WV stands for "working voltage", it is essentially the max voltage that the capacitor should handle.

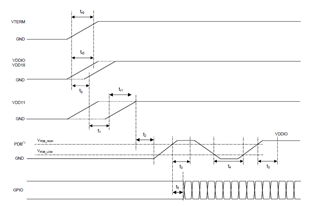

2) We do not have a recommended sampling time for those capacitors, I would recommend looking at section 9.1 in the datasheet where it goes over the recommended power-up sequence. After a PDB reset, there is no additional wait time needed.

Please let me know if you have any other questions.

Best,

Cameron Carlson

thanks Cameron

question2, I want to know 0.1uF, if RC need long time, example R3 =118K, R4 = 30.9K, so RC = 118*0.1,it need time for charge the 0.1uF, i want to know the time for IC internal sampling these, it must bigger than RC charge time.

Hi Songlin,

I am going to consult with my team about this and get back to you after July 4th.

Best,

Cameron Carlson

Hi Songlin,

So long as you are following the recommended power-up sequence, it will already cover the sample time for these pins.

One way to double check is to read registers 0x00 and 0x5B. Register 0x00 will give the device ID, which will show whether or not your IDX pin is strapped correctly. Bit 7 of register 0x5B will give the FPD3 Coax Mode, if this is read correctly, then it will verify that your mode_straps are set correctly. As mentioned before, this is only to double check as the device will already cover the sampling time for these pins if the recommended power-up sequence is followed.

Please let me know if you have any other questions.

Best,

Cameron Carlson

it will already cover the sample time for these pins.

when power up, it will need time to sampling

After a PDB reset, there is no additional wait time needed.

after PDB, it's sampling ok? so time between power up VDDIO and PDB the sampling down ? but t2 minimal 0ms.

Hi Songlin,

Per the datasheet sampling, the PDB signal must go high after the power rails are stable and high. After this point, yes, sampling is okay.

Best,

Cameron Carlson

Hi Songlin,

There is no sampling time for powering on the device, as there isn't a set polling/sampling rate that the device checks PDB at.

Please refer to the power sequencing for proper operation of the device. PDB must be high after power supplies are fully high and stable (>0ms), but outside of this there is no sampling time requirements from VDD to PDB high.

so time between power up VDDIO and PDB the sampling down ? but t2 minimal 0ms.

T2 indicates PDB needing to go high after VDD rise.

Best,

Cameron Carlson

Still don't understand this, when power up, it will need maybe 1ms for sampling IDX or MODE_SEL pin value?

Hi Songlin,

There is a 2ms delay time required between PDB high and programming the device.

Otherwise, we do not characterize a "sampling time". As long as PDB is high only after VDD stable (represented by T2) and 2ms is waited before programming I2C (represented by T3); then all sequencing and sampling requirements are statisfied concerning PDB.

Regards,

Logan

Hi Songlin,

Yes, 0.1uF is what we recommend for those pins for any pullup resistors specified in the datasheet.

Best,

Holly Roper