Other Parts Discussed in Thread: STRIKE

Is there a risk of latch-up with ESD diodes? Should this be taken into design consideration?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: STRIKE

Is there a risk of latch-up with ESD diodes? Should this be taken into design consideration?

In the context of ESD, latch-up is the condition where the protection device experiences electrical overstress because of continuous conduction after an ESD strike has passed. This can damage the ESD diode and compromise signal transmission.

In summary, a shallow snap-back diode will not incur latch-up if operated under the rated reverse working maximum voltage (VRWM). However, with deep snap-back diodes, latch-up is possible after an ESD strike when the line voltage is above the holding voltage (VHold), and when the line current is above the holding current.

More details below:

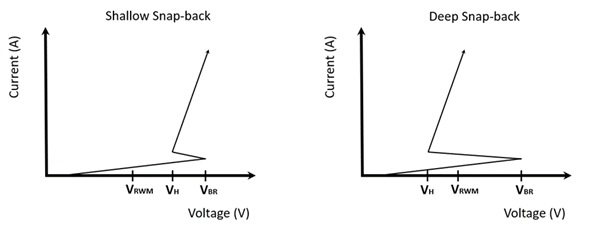

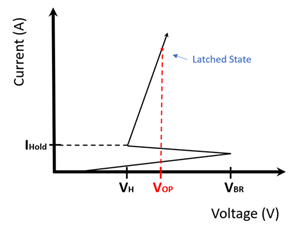

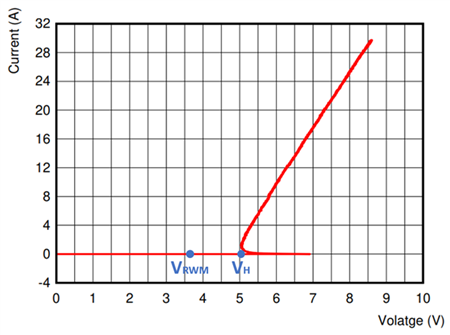

During an ESD strike, ESD diodes can exhibit a temporary negative resistance in which the voltage “snaps back” to the holding voltage. Two example IV graphs with the holding voltage (VH) and reverse working voltage (VRWM) are shown below.

Snap-back is the difference between VH and VBR, and there is both shallow (left) and deep snap-back (right). Deep snap-back is beneficial when a lower clamping voltage is desired. However, deep snap-back has the highest risk of incurring latch-up.

Notice where VRWM is marked on both graphs above. In the case of the shallow snap-back diode (left), VRWM is lower than VH. For the deep snap-back (right), VRWM is higher than VH.

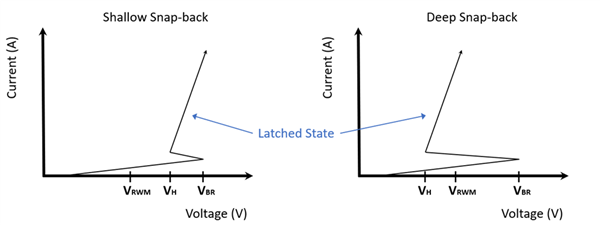

During an ESD strike, when the voltage level exceeds the voltage breakdown (VBR, also known as a voltage trigger), snap-back occurs and the diode shunts the current to ground as designed. During this time, the diode briefly enters the latched state where the dangerous levels of current are shunted away from the protected system. This lasts anywhere from the nanosecond to microsecond time frame.

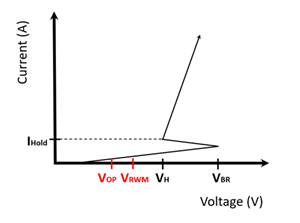

Shallow Snap-Back:

In the case of shallow snap-back ESD diodes, VH is significantly higher than the operation voltage (VOP) so there is no risk of latch-up.

When selecting ESD diodes to protect a system for either types of snap-back, VOP should not exceed VRWM.

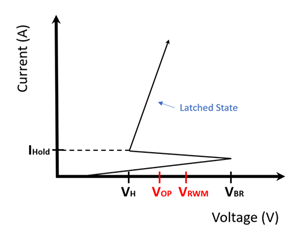

Deep Snap-Back:

Deep snap-back diodes must be approached differently. When a device routinely operates in between VH and VBR, there is a chance it will stay in the latched state after a trigger event such as an ESD strike.

A deep snap-back device will latch-up under these conditions: the diode finished conducting the ESD strike, the voltage on the line stays above the VH, and the current on the line is above the holding current (IHold). If the voltage does not drop below VH after an ESD strike, the diode will continue shunting current to ground.

When latch-up occurs, there can be a soft or hard failure. A soft failure can be reset when the data line returns to a low or recessive state (i.e. 0 bit). A hard failure is when the diode is permanently damaged due to a high current sustained over a long period of time. This leaves the system unprotected since ESD diodes are not designed to sustain current above IHold for extended periods of time.

Example:

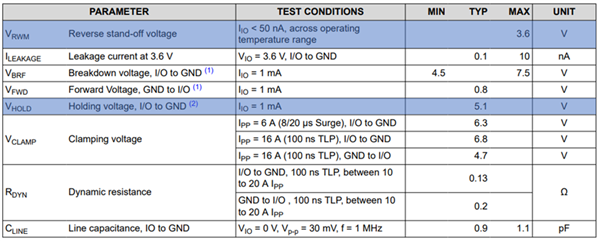

To determine if a diode is at risk of latch-up, let’s take ESD321 as an example. To find the type of snap-back variation, observe the highlighted electrical characteristics below.

Here we can notice that VRWM is 3.6V and VHold is 5.1V. Since VRWM is less than VHold, this device has shallow snap-back. There is no risk of latch-up assuming the operational voltage does not exceed VRWM.

Additional Resources