Part Number: DS90UB935-Q1

Hi team,

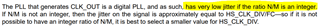

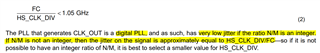

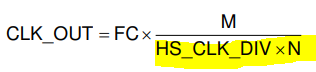

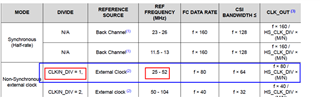

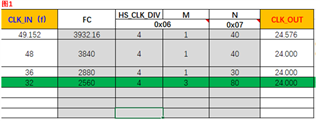

my customer use this mode, CLK_IN configured as 32MHz input,

use below marked GREEN to create CLK_OUT=24MHZ

then they test 32MHz active crystal : AVG: 31.997MHz, MAX: 32.051MHz, MIN: 31.948MHz.

The test CLK_OUT is 23.75MHZ~24.25MHZ.Is this error within reasonable limits? If not, please help to analyze the cause of this large error

thanks