Hello,

we are developing a product with DS90UB949A, which should support pixel clock up to 210 MHz, however we are struggling to go beyond 165 MHz.

We have a display with 948 deserializer (max PCLK 190 MHz) and a mating car control unit with 949A, which gives video signal with PCLK=178,42 MHz. Therefore; the display is capable of recieving such signal and 949A is capable of generating such signal, but we don't which configuration/operating mode is used.

We captured timing with an analyzer to created an EDID structure with matching parameters.

We discovered, that any EDID structure with PCLK greater than ~165 MHz won't work with the display and this behavior is the same our custom PCB and the EVM as well. In case the PCK is greater than 165 MHz, the 949A doesn't propagate the custom EDID to GPU drivers (949A reports VGA resolution or isn't recognized at all depending on the GPU/driver vendor). We made an EDID with 55 FPS which works fine. However, attempts with 56 FPS or greater have been failing.

EDID:

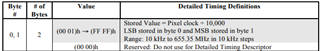

0x00, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0x00, 0x53, 0x0E, 0x49, 0x09, 0x01, 0x00, 0x00, 0x00,

0x1C, 0x21, 0x01, 0x03, 0x80, 0x34, 0x20, 0x78, 0x0A, 0xEC, 0x18, 0xA3, 0x54, 0x46, 0x98, 0x25,

0x0F, 0x48, 0x4C, 0x00, 0x00, 0x00, 0x01, 0x01, 0x01, 0x01, 0x01, 0x01, 0x01, 0x01, 0x01, 0x01,

0x01, 0x01, 0x01, 0x01, 0x01, 0x01, 0xE3, 0x3F, 0xC0, 0x60, 0x80, 0xEC, 0x0D, 0x40, 0x1C, 0x1C,

0x62, 0x00, 0x00, 0x20, 0x21, 0x00, 0x00, 0x18, 0x00, 0x00, 0x00, 0xFC, 0x00, 0x57, 0x56, 0x5F,

0x31, 0x35, 0x5F, 0x30, 0x5F, 0x48, 0x34, 0x31, 0x0A, 0x20, 0x00, 0x00, 0x00, 0xFE, 0x00, 0x54,

0x45, 0x53, 0x54, 0x45, 0x32, 0x30, 0x32, 0x33, 0x30, 0x37, 0x31, 0x37, 0x00, 0x00, 0x00, 0x10,

0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0xC0,