Other Parts Discussed in Thread: DS90LV049, THVD1452, THVD1552, SN65LVDS049

Hello TI team ,

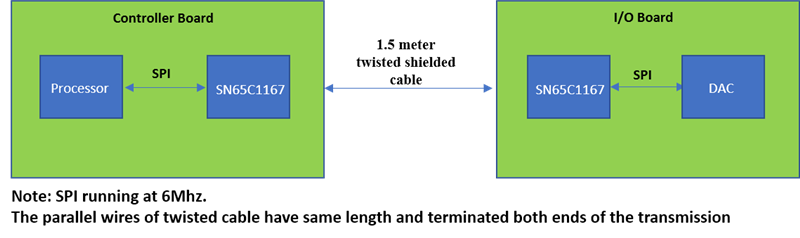

I want to implement the below architecture based on the article http://www.ti.com/lit/an/slyt441/slyt441.pdf

The query is :

1. Currently the below use case is designed to work at SPI data rate of 6Mhz. Is it fine for 20Mhz or 50Mhz ?

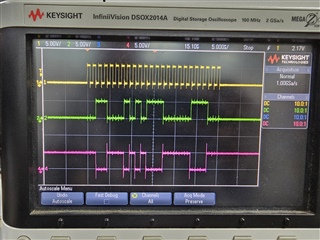

2. When decoding the SPI line (MOSI) at the processor side, data which iam trying to send to the I/O board is perfect. But when i decode the SPI line (MOSI) at the DAC input, the data received there is totally different.

For ex: Data iam sending is "FF DC". But data received at the DAC input side is "00 80". Why is it happening like that? Do i need to reduce the SPI data rate below 6Mhz?

Can you please look into the same ....