Other Parts Discussed in Thread: ALP, USB2ANY

Hi Team

there is one question on FPDlink clock.

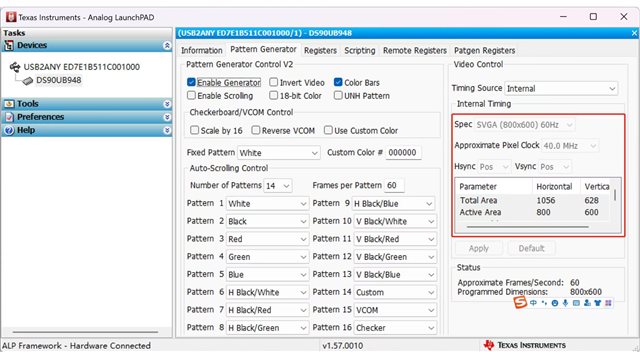

How can I calculate the real oLDI PCLK according to the PCLK set in ALP?

Use PC as host and USB2ANY connected to 948, use the pattern mode, set the PCLK in ALP to 40MHz the tested oLDI output is 27MHz, use the single port output mode of 948.

You can see the setting in the picture below:

Thank you

best regards

Joe

JUL 24