Other Parts Discussed in Thread: ALP, USB2ANY

To whom this may concern,

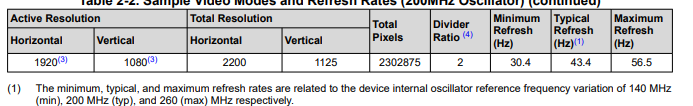

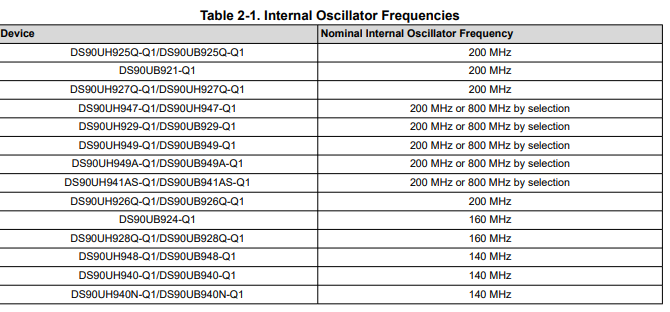

I am trying to use the DS90UB948-Q1EVM eval board with a 1080p 60Hz display. I was able to get the pattern generator to display images on the screen, but a few artifacts are present. Notably, there are two columns of horizontal pars that run down the middle of the screen. It also appears that the picture on one side of the screen is inverted (this can be seen when generating the VCOM pattern).

I've connected the eval board to the screen with the following LVDS configuration:

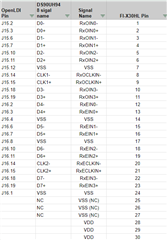

I'm using the AUO G173HW01 V0 display, with 2-port LVDS interface. Here's the pinout of the display connector:

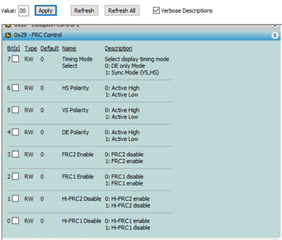

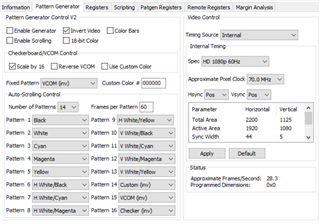

These are the ALP parameters I'm using:

I'm currently operating with switch S1 (MODE_SEL0) setting as S1.7 on, all others off. I've attached an image of the evaluation board:

Do you have any idea as to what could be causing the artifacts?

Regards,

Alex