Hello, I was working on the configurations for standby and normal mode.

Whenever I try to configure the device into standby mode I follow these steps:

void BusSleepMode::ConfigureETHPhytoStandbyMode(void)

{

uint16_t registerData = 1U;

registerData = registerData<<7U;

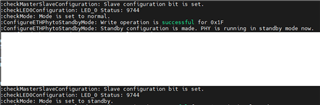

if(WRITE_STATUS_OK == Phy_write_register(0x1FU, registerData))

{

// Readback the register to check operation is successful or not.

if(READ_STATUS_OK == Phy_read_register(0x1FU, ®isterData))

{

if(1U == ((registerData>>7U) & 0x0001U ))

{

LOGI(&gETHNM_Log_ctx, "Write operation is successful for 0x1F");

while(contextInstanceSM.getETHPhyResetStatus() == false)

{

// Write to 0x18C '10000b' which is equal to 0x10

static_cast<void>(MMD1F_write_register(0x18CU, 0x0010U));

uint16_t readBack;

static_cast<void>(MMD1F_read_register(0x18EU, &readBack));

LOGD(&gETHNM_Log_ctx, "READBACK FOR STANDBY: ", readBack);

if(1U == ((readBack>>1U) & 0x0001U))

{

contextInstanceSM.setETHPhyResetConfigurationFlag();

LOGI(&gETHNM_Log_ctx, "Standby configuration is made. PHY is running in reset mode now.");

break;

}

else

{

LOGE(&gETHNM_Log_ctx, "Standby configuration is failed.");

}

std::this_thread::sleep_for(std::chrono::milliseconds(10));

}

}

}

}

else

{

LOGE(&gETHNM_Log_ctx, "Write register to 0x1F returned fail.");

}

}void NetworkMode::ConfigureETHPhytoNormalMode(void)

{

uint16_t registerData = 0U;

registerData = registerData<<7U;

if(true == contextInstanceSM.getETHPhyResetStatus())

{

// Clear out the register data.

if( WRITE_STATUS_OK == Phy_write_register(0x1FU, registerData))

{

if(READ_STATUS_OK == Phy_read_register(0x1FU, ®isterData))

{

if(0U == ((registerData>>7U) & 0x0001U ))

{

LOGI(&gETHNM_Log_ctx, "Read operation is successful for 0x1F. Bit is cleared.");

while(contextInstanceSM.getETHPhyResetStatus() == true)

{

// Write 0x18C to '1b' to set the normal mode.

static_cast<void>(MMD1F_write_register(0x18CU, 0x0001U));

uint16_t readBack;

static_cast<void>(MMD1F_read_register(0x18EU, &readBack));

LOGD(&gETHNM_Log_ctx, "READBACK FOR NORMAL: ", readBack);

if(1U == ((readBack>>2U) & 0x0001U))

{

contextInstanceSM.clearETHPhyResetConfigurationFlag();

LOGI(&gETHNM_Log_ctx, "Reset configuration is cleared. PHY is running in normal mode.");

break;

}

else

{

LOGE(&gETHNM_Log_ctx, "Reset configuration is failed.");

}

std::this_thread::sleep_for(std::chrono::milliseconds(10));

}

}

}

}

else

{

LOGE(&gETHNM_Log_ctx, "Write register to 0x1F returned fail.");

}

// Set the link status up by using ioctl functions

changeLinkStatus("eth0");

changeLinkStatus("vlan1");

}

}