Dears:

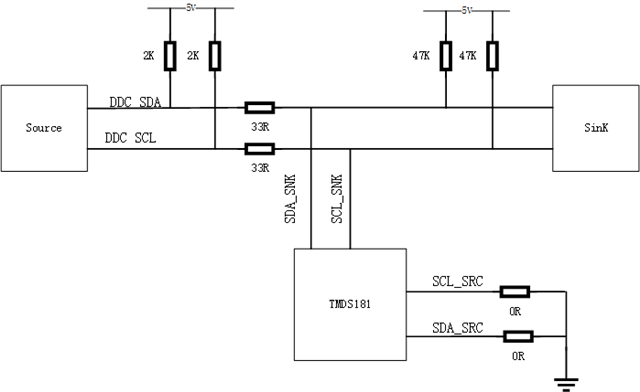

The picture shows two connection modes of DDC circut

Paranormal:The display appears unusually at 4k@60hz resolution,When DDC circuit in accordance with Figure 1;

But the display appears normally at 4k@60hz resolution,When DDC circuit in accordance with Figure 2.

The display appears normal in both connection modes at 4k@30hz resolution.

I want to know:

What causes the discrepancy?

What‘s the reason that the display appears unusually when the normal EDID information is obtained in fig 1?