Part Number: TCAN4550EVM

Other Parts Discussed in Thread: TCAN4550, , TCAN4550-Q1

Hello,

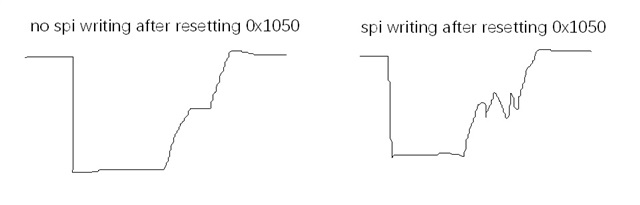

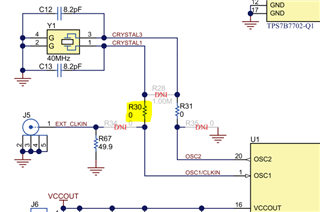

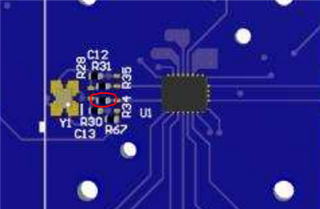

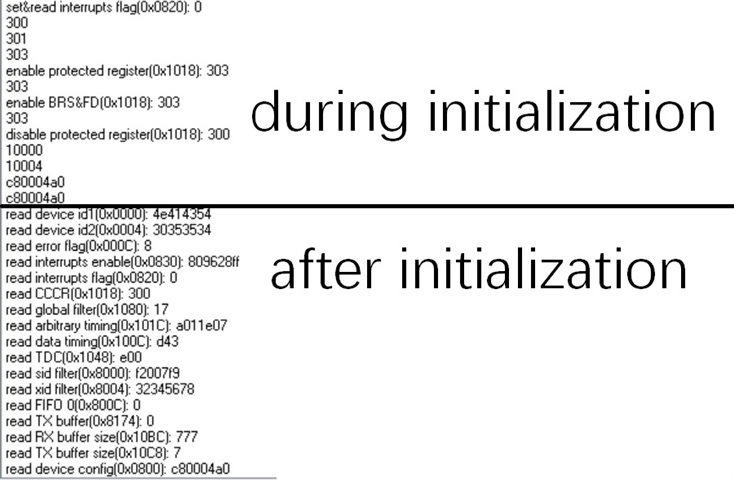

with your help from my last post, I'm able to establish contact with TCAN. Then I tried to 'translate' your code sample to keil code for ST MCU. The initialization was failed. Other CAN devices get no ACK from TCAN. I got a 'Internal Multiple transfer mode access in progress' error immediately after I tried to clear all errors. I recorded the read values from the registers I wrote to in the screenshot. Can you see anything wrong?

What I've done is:

write '0xFFFFFFFF' to 0x000C (clear ERR flags)

write '0' to 0x0830 (disable interrupts)

read from 0x0820 and write this value back (clear the interrupt flags)

write '0' to bit 4&3 and '1' to bit 1&0 of 0x1018 (enable protected register)

read from 0x1018, apply mask (~(0xFFFF0C00 | 8)), set '1' to bit 9,8,1,0, and write back (enable BRS, FD, CCE, INIT)

write '1' to bit 4,2,1,0 of 0x1080 (accept global messages to FIFO0)

write '5<<25 | 1<<16 | 30<<8 | 7' to 0x101C (SJW=6, prescaler=2, tseg1=31, tseg2=8)

write '0<<16 | 13<<8 | 4<<4 | 3' to 0x100C (prescaler=1, tseg1=15, tseg2=5, SJW=4)

write '14<<8' to 0x1048 (TDCO=15)

write '0' to memories from 0x8000 to 0x87FF (clear memories)

write '0' to 0x1084 (standard filter address = 0x8000)

write '4' to 0x1088 (extended filter address = 0x8004)

write '0x800C | 5<<16 | 0x80000000' to 0x10A0 (RX FIFO0 elements =5, address =0x800C)

write '0x8174 | 0<<16 | 0x80000000' to 0x10B0 (RX FIFO1 elements =0, not used)

write '0x8174' to 0x10AC (RX buffer elements =0 , not used)

write '0x8174 | 0<<16' to 0x10F0 (RX buffer elements =0, not used)

write '0x8174 | 2<<24 ' to 0x10C0 (TX buffer elements =2, address =0x8174)

write '7<<8 | 7<<4 | 7' to 0x10BC (RX buffer size = 64 bytes)

write '7' to 0x10C8 (TX buffer size = 64 bytes)

write '0' to bit 4,3,1,0 of 0x1018 (disable protected register)

write '1' to 0x1054 (enable RX FIFO0 interrupt on nINT)

write '0<<30 | 1<<27 | 0x720<<16 | 0x7F9' to 0x8000 (standard id filter: SFT=0(range filter), SFT=1(store in FIFO0), SID1=0x720, SID2=0x7F9)

write '1<<29 | 0x12345678' to 0x8004 and '2U<<30 | 0x1FFFFFFF' to 0x8008 (xid filter: EFEC=1, id=0x12345678, EFT=2, mask=0x1FFFFFFF)

write '3U<<30| 1<<27 | 1<<10 | 1<<5' to 0x0800 (device config register)

write '2' to bit 7&6 of 0x0800 (normal mode)

write '0xFFFFFFFF' to 0x1050 (clear all interrupts)