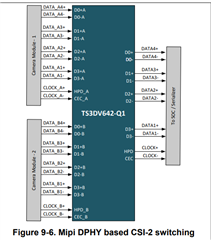

Part Number: TS3DV642-Q1

Hello team,

I had few queries regarding TS3DV642-Q1. We are using this as MIPI MUX.

1. In the general application, it is shown as HPD_A can be used for CLK+.

However, we are using CEC for CLK+.

Please confirm if it is okay.

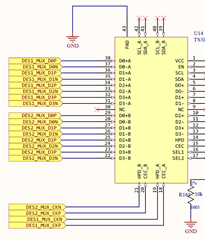

2. Currently, data signals and clock signals co-incide, hence via is taken for clock signal. Is this recommended?

3. What should be the maximum length difference between CLK/D+ and CLK/D- signals of differential pair.

4. Can clock signals be routed through Data pins of MUX if they are identical in functionality? This is to reduce the routing complexity.