Part Number: DP83869HM

Other Parts Discussed in Thread: DP83869

To whom it may concern -

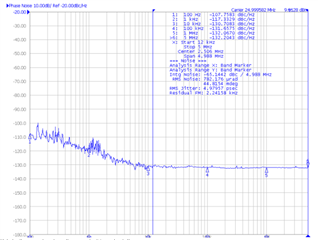

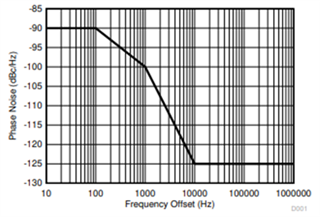

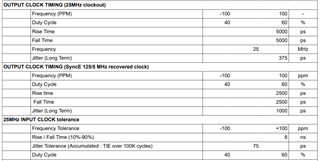

Per the datasheet, it states "By default, the output clock is synchronous to the XI oscillator / crystal input. The default output clock is suitable for use as the reference clock of another DP83869HM device." However, when we have one DP83869 Clock Output go to another DP83869 Clock Input, the jitter spec implies that it is not compatible:

Specifically, the Output Clock 25MHz Jitter is 375ps (max), whereas the Input Clock Tolerance is 75ps (typ). Is that correct or is my interpretation of this table incorrect?

Thanks,

Brendan