Hi Team,

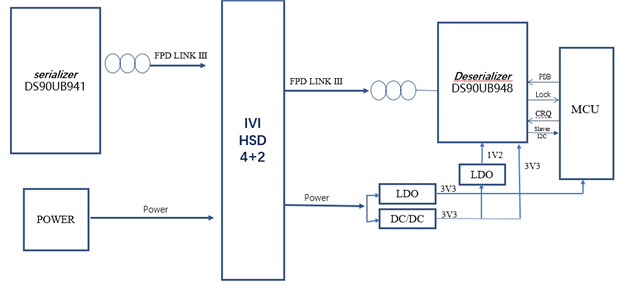

TI941 with TI948, a 941 read could not find 948 during use, and normal communication could not be established, resulting in a black screen.

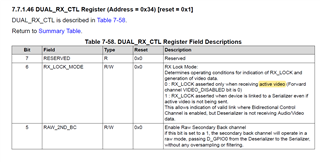

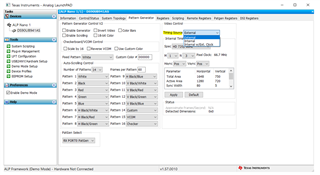

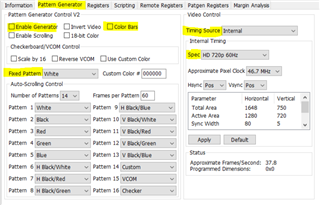

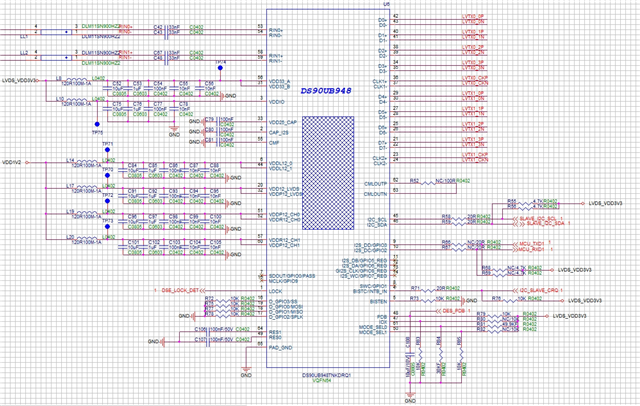

The customer deserializer TI948 circuit is a two-channel LVDS input and two sets of OLDI outputs of 1lane+4lane. The serializer chip used on the host side is TI941. The above issue occurs during real use and currently the bench test does not occur, so no valid exception information is available. Could you please help check out if this is TI948-related-circuit issue?

Could you help check it? Thanks.

Best Regards,

Cherry