Other Parts Discussed in Thread: DS90UB926Q-Q1, MIDAS

Hello

- We are trying to use the MIPI DSI signals to drive our display, setup below

Hardware Setup: Quectel SMART-EVB-G2_V1.3 (with SC668S-EM) >>> DS90UB941AS-Q1 (Serializer)>>>via FPD3>>>DS90UB926Q-Q1 (Deserializer)>>>RGB 800x480 Display

What we’ve done so far:

- Use the display driver guide to modify the dtsi files according to the quectel guide (spreadsheet) attached. The following display timing parameters are used:

H = 800

HFP = 44

HSW = 50

HBP = 38

V = 480

VFP = 8

VSW = 3

VBP = 29

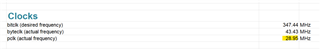

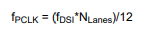

Pixel clock = 33 MHz

- For our setup, we’ve determined that changing ili9881 related dsi parameters are needed to have discernable difference.

- Once we’ve changed these two files and rebuilt the android image the touchscreen that it came with stopped working properly as expected; because the timings are different.

- On the serialiser side, we’ve set the following registers:

- MODE SEL [1:0] – this is done via resistors (page 38 of serialiser datasheet)

The current setting is Splitter=0, DSI lanes=4, Clock=1 (FPD link is generated from DSI clock, DSI clock has to be in continuous mode), COAX=0 i.e. twisted pair cabling, DSI=0 i.e. enabled.

- Setup registers set for sync width config as described in page 17 of SNLA356 guide attached

bufW[0]=0x40; //put port select in indirect register 0x40

bufW[1]=0x04; //set port 0

bcm2835_i2c_write(bufW,2);

bufW[0]=0x41; //put address in indirect register 0x41

bufW[1]=0x30; //DSI_HSW_CFG_HI

bcm2835_i2c_write(bufW,2);

bufW[0]=0x42; //put data in indirect register 0x42

bufW[1]=0x00; //DSI_HSW_CFG_HI=0

bcm2835_i2c_write(bufW,2);

bufW[0]=0x41; //put address in indirect register 0x41

bufW[1]=0x31; //DSI_HSW_CFG_LO

bcm2835_i2c_write(bufW,2);

bufW[0]=0x42; //put data in indirect register 0x42

bufW[1]=0x30; //DSI_HSW_CFG_LO=0x30 (48)

bcm2835_i2c_write(bufW,2);

bufW[0]=0x41; //put address in indirect register 0x41

bufW[1]=0x32; //DSI_VSW_CFG_HI

bcm2835_i2c_write(bufW,2);

bufW[0]=0x42; //put data in indirect register 0x42

bufW[1]=0x00; //DSI_VSW_CFG_HI=0

bcm2835_i2c_write(bufW,2);

bufW[0]=0x41; //put address in indirect register 0x41

bufW[1]=0x33; //DSI_VSW_CFG_LO

bcm2835_i2c_write(bufW,2);

bufW[0]=0x42; //put data in indirect register 0x42

bufW[1]=0x03; //DSI_VSW_CFG_LO=3

bcm2835_i2c_write(bufW,2);

bufW[0]=0x40; //put port select in indirect register 0x40

bufW[1]=0x04; //set port 0

bcm2835_i2c_write(bufW,2);

bufW[0]=0x41; //put address in indirect register 0x41

bufW[1]=0x20; //DSI_CONFIG_0

bcm2835_i2c_write(bufW,2);

bufW[0]=0x42; //put data in indirect register 0x42

bufW[1]=0x6F; //DSI_SYNC_PULSES=0

bcm2835_i2c_write(bufW,2);

- Dsi lane config registers to match hardware connections.

- I’ve attached the specs/datasheets accordingly. But unfortunately, the display is not working (we just see a black screen), perhaps you can help us toward the right direction.

Maybe there’s a guide/tutorial that you have that’s applicable to our setup?

Thank you for your time and efforts.

MDT0430E5IHHC-RGB.pdfQuectel_SC668S_Series_Display_Driver_Development_Guide_V1.0.pdf snla356 user guide.pdf

snla356 user guide.pdf