Part Number: DS90UB941AS-Q1

Hi Team,

The customer uses an internal pattern generator to test if the hardware connection between master and slave is correct. Follow the "internal test pattern generation feature of the explore FPD-Link III IVI device", but it does not appear to have any graphic display on the screen. Could you please help check if the register configuration and flow are correct or complete:

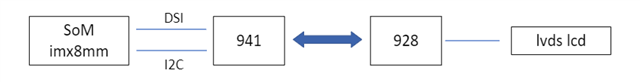

A simplified connection diagram is shown below and the LCD display is now debugged first:

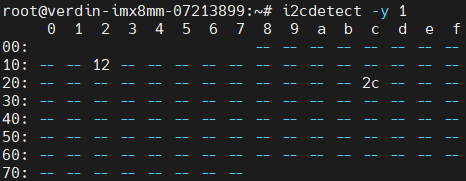

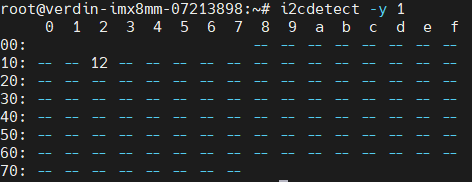

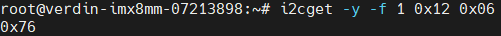

After starting the board, using i2c-tools, it can be seen that the 941 device address is 0x12:

I2C_BUS_NUMBER=1

941_ADDR=0x12

Reading des_ID_des_ID_1 register 0x06 has a value of 0x76, and shifting right by one bit results in a 928 deserializer ID of 0x3B:

Then execute the script for the register configuration of the pattern generator, “941as_800x480p_PATGEN.sh”, using the internal timing and the internal pclk:

#!/bin/bash

# 800x480p60, Dual Link FPD III

# PCLK = 33.264MHz

# DSI clock = 99.792MHz

# DSI Lane Speed = 199.584Mbps/lane

# 4 Lanes DSI

# DSI input port 0

# Pattern Generator Mode

# Internal clock and Internal

# use i2c-tools to debug

set -e

I2C_BUS_NUMBER=1

UB941AS_ADDR=0x12

# Reset

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x01 0x02

# sleep 0.1s

sleep .1

# Disable DSI

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x01 0x08

# Select FPD-Link III Port 0 (default port0)

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x1E 0x01

# 1. Set Pixel Clock and Active Frame Size

# pixe clock = 33.264MHz divider = 200/33.264 ≈ 6

# hactive = 800 vactive = 480

#

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x66 0x03

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x67 0x06

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x66 0x07

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x67 0x20

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x66 0x08

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x67 0x03

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x66 0x09

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x67 0x1E

# 2. Set Total Frame Size

# Total H Width = 40(hback porch) + 800(hactive) + 40(hfront porch) + 48(hsync len)

# = 928 = 0011 1010 0000

# Total V Width = 31(vback porch) + 480(vactive) + 13(vfront porch) + 1(vsync len)

# = 525 = 0010 0000 1101

#

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x66 0x04

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x67 0xA0

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x66 0x05

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x67 0xD3

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x66 0x06

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x67 0x20

# 3. Set Back Porch

# H Back Porch = 40 = 0010 1000

# V Back Porch = 31 = 0001 1111

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x66 0x0C

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x67 0x28

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x66 0x0D

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x67 0x1F

# 4. Set Sync Widths

# H Sync Width = 48 = 0011 0000

# V Sync Width = 1 = 0000 0001

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x66 0x0A

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x67 0x30

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x66 0x0B

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x67 0x01

# 5. Set Sync Polarities

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x66 0x0E

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x67 0x00

# 6. Enable Pattern Generation

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x65 0x03

i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x64 0x11

Could you please help check this case? Thanks.

Best Regards,

Cherry