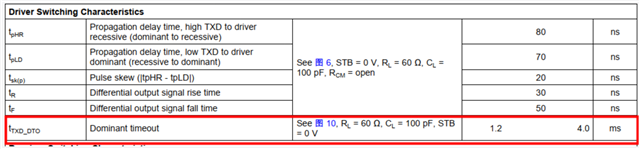

Part Number: TCAN1044AV-Q1

Hi,all

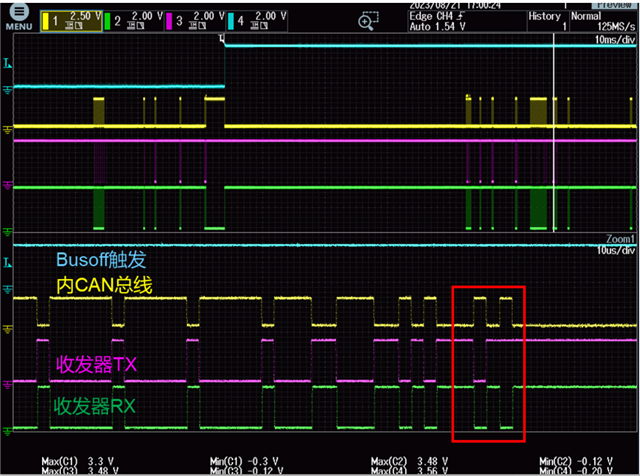

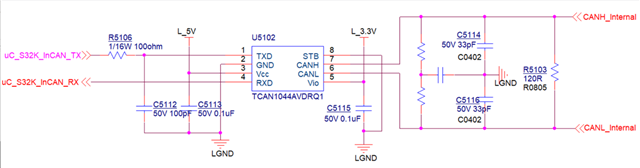

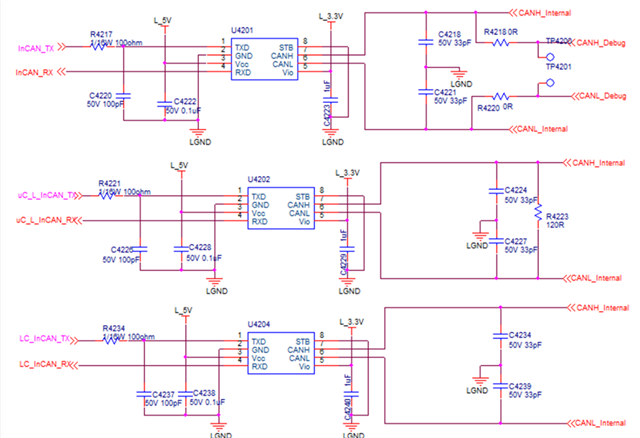

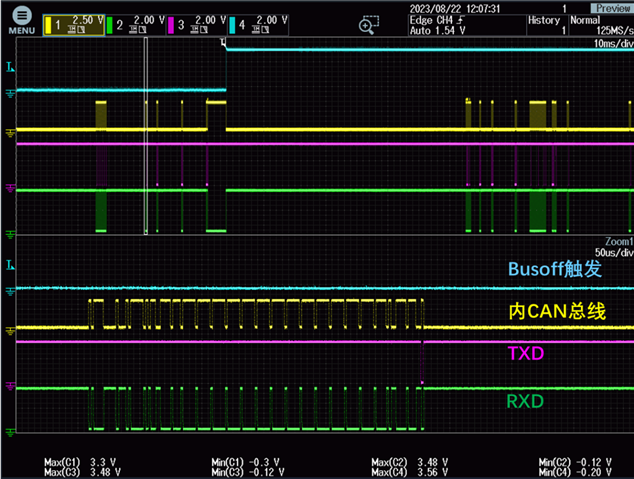

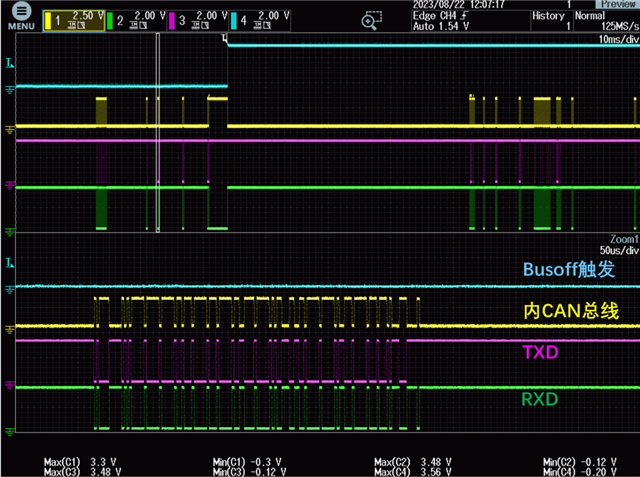

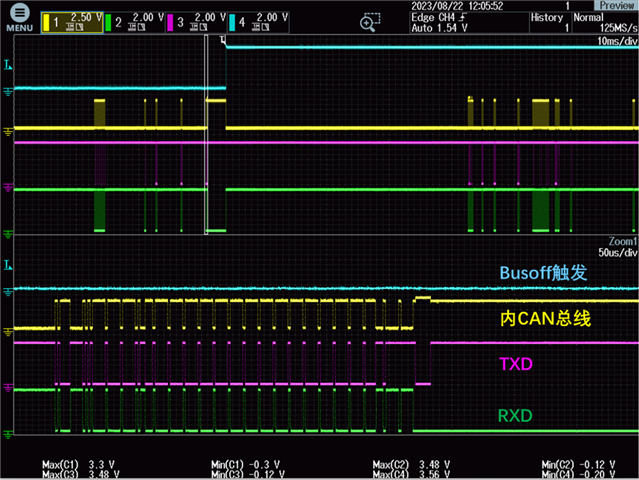

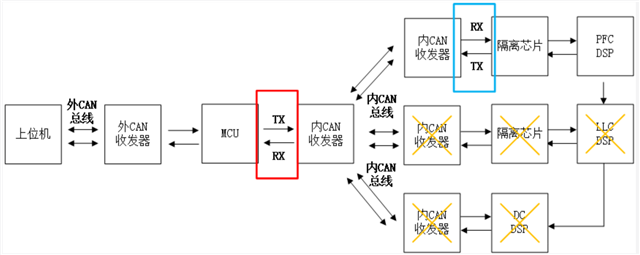

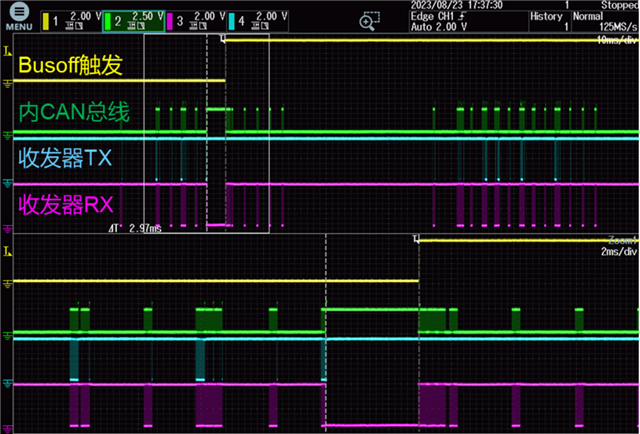

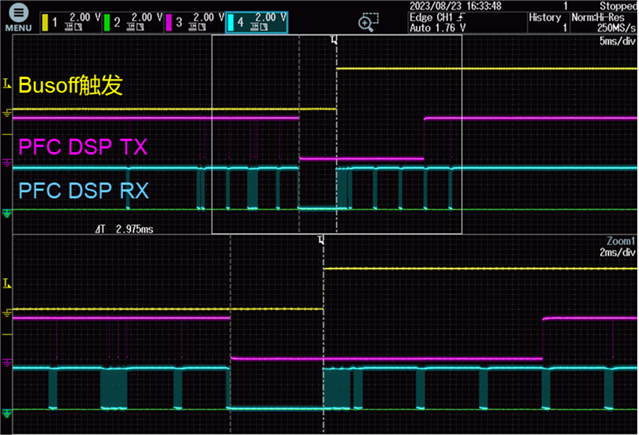

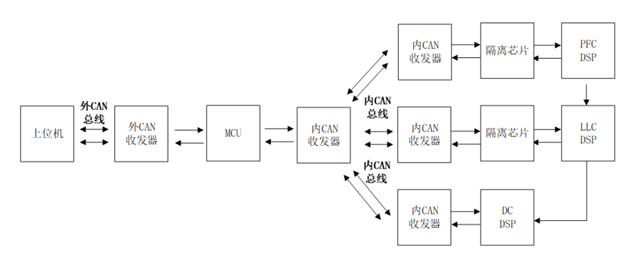

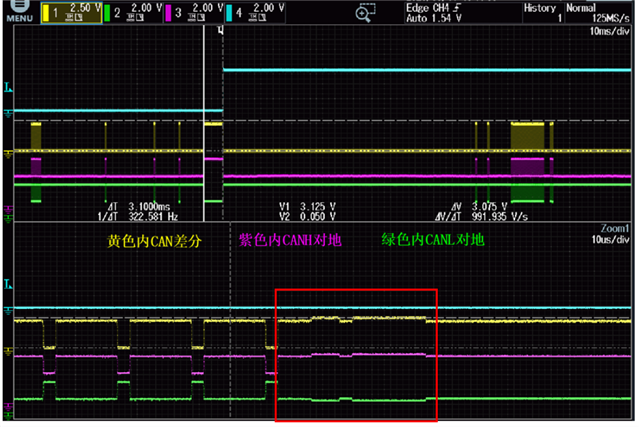

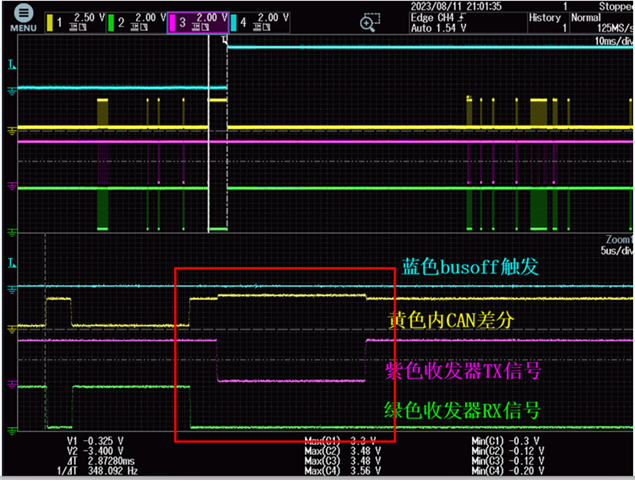

Problem background: The communication structure is shown in Figure 1. When the upper computer sends instructions, the CAN bus will trigger bus busoff for some reasons, resulting in the bus failing to receive subsequent instruction delivery. After finding out the reason, it is found that the communication signals on the CAN bus and between the MCU and the CAN transceiver are interfered, as shown in Figure 2 and Figure 3, and Figure 4 is the signal normally transmitted by the bus. The blue waveform in Figure 3 is the GPIO state of MCU, and the logic is that the level is flipped once when busoff is encountered, which is used to capture other signals in the moment triggered by busoff. The CAN bus state is consistent with the RX level, indicating that the CAN bus is in the state of transmitting DSP data back to the MCU at this time, because the abnormal RX signal causes the MCU to recognize the BUSOFF and close the bus.

Requirement 1: In the red box as shown in Figure 2, does TCAN1044 have any mechanism that will affect the CAN bus level?

Requirement 2: As shown in the red box in Figure 3, CAN bus is in the state of returning data, and the level is slightly elevated. How is this abnormally elevated part affected? Will it be caused by the low level signal of TX?

Requirement 3: As shown in Figure 3, when the MCU is sending data and receiving the return data at the same time, the bus is in the return state. At this time, can the bus receive the data sent by the MCU to the bus?

Picture 1:

Picture 2:

Picture 3:

Picture 4: