Other Parts Discussed in Thread: AM68A, CDCE6214

We like to use a DS90UB953 in DVP mode togehter with a DS90UB914A deserializer. Unfortunately, our AM68A CSI interface has neither a synchronised clock output nor a reference clock input.

How can we achieve a synchronized clock, which is mandatory for DVP mode? Do we have to use e.g. a CDCE6214 clock generator IC and derive a synchronized clock? Or is there a much smarter solution?

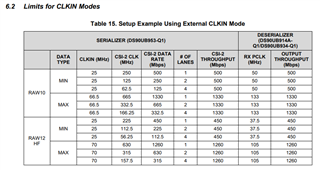

A second question is about the calculation of frequencies and througput. Are these values correct?

On deserializer side (914A) we like to achieve a 65 MHz PCLK. With "RX PCLK/CLKIN = 1.5 in RAW12 HF" the CLKIN (UB953) shall be 43.3 MHz (65/1.5) ?

The total required (CSI-2) throughput is 65MHz * 12Bit = 780 Mbps?

Best,

Martin