Other Parts Discussed in Thread: DP83869

Hi,

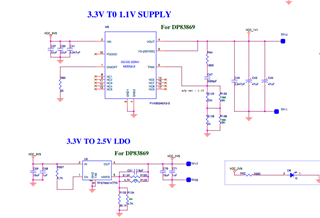

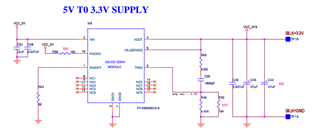

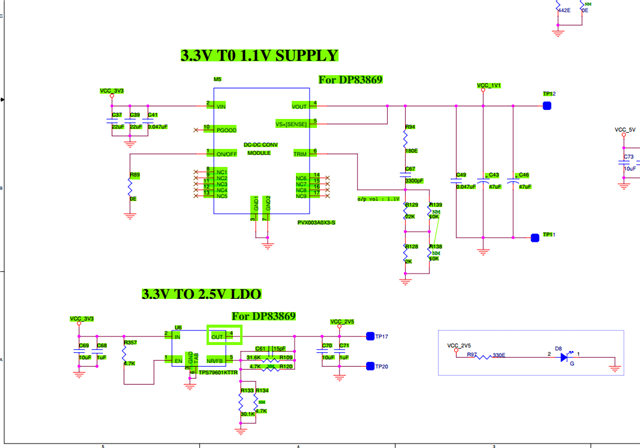

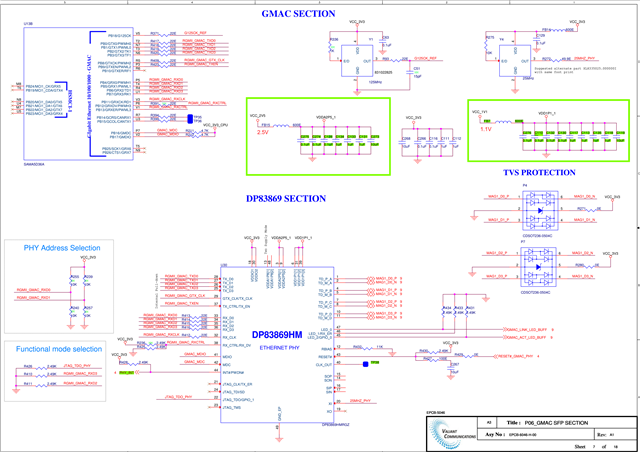

We are using DP83869 in our design. Please find the schematics as per the attachment.

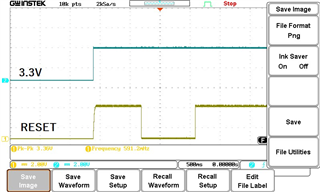

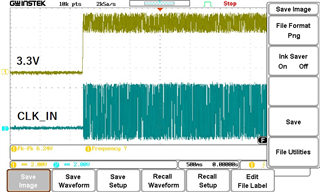

While powering ON our observation :

2.5V rail is getting 3.1V

When ALL RAILS are connected , at 3.3V we are getting 3.3v, BUT at 2.5V rail we have observed 3.1V. \

We have checked the source LDO 2.5V by removing the FB15.

We are getting 2.5V properly.

While debugging, in one card we have removed the DP83869, we are getting all voltages properly till the pads of U30.

When chipset is mounted condition, & FB15 removed in this point && When 3.3V RAIL alone connected irrespective external circuitry we are getting 3.1V at the VDDA2P5_1

Please revert back for any queries. PLease support us

Regards

Guru sai prasanth