Part Number: DP83869HM

Other Parts Discussed in Thread: DP83869

Hello,

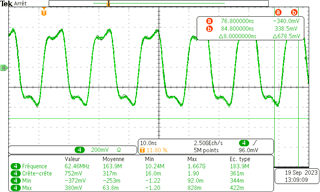

DP83869 is used in rgmii copper mode, connected to a SOC through rgmii/mdio, on a custom board.

Linux driver is used on the SOC. PHY initialization seems ok (detection on mdio, configuration).

Default configuration is used.

PHY LED configuration has been changed to have link-up / tx activity only / rx activity only.

- Cable connection between the custom board and a PC :

link-up LED becomes stable ON.

PC indicates link-up, auto-negotiated 10Mbps - full, the SOC too.

- Ping from PC:

rx LED blink

tx LED blink

tcpdump on the SOC displays the ARP received from the PC and the answers sent back to it.

PC does not receive the answers. ping fails.

- Ping from SOC:

rx LED off

tx LED blink

PC does not receive the ARP requests. ping fails.

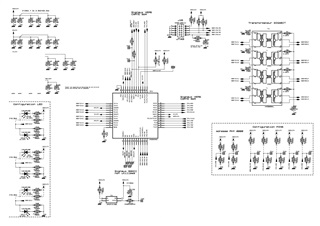

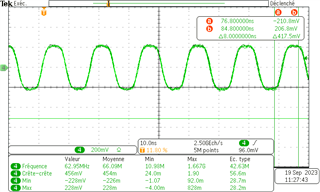

CLK_O_SEL (IO_MUX_CFG register) has been modified to monitor TX clock on scope:

Channel A transmit clock: CLK_OUT = 25MHz

Channel B transmit clock: CLK_OUT = 25MHz

Channel C transmit clock: CLK_OUT = 25MHz

Channel D transmit clock: CLK_OUT = 25MHz

Default configuration (ref clock): CLK_OUT = 25MHz

Shoud we have 2.5MHz since the link is 10Mbps?

Can we say RX is ok ? SOC-PHY connection is ok ?

I don't know where is the issue, what I have to check and the tests I could do...

I can provide PHY register values if needed.

Thanks for your help.