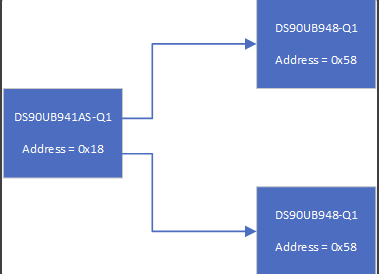

Part Number: DS90UB941AS-Q1

At present, our company has encountered the following issues while debugging the TI941+TI948 split screen scheme:

The overall block diagram is as follows:

941 Configuration:

0x1E, 0x01, port0

0x03, 0x9a, pass_ Through

0x1E, 0x02, port1

0x03, 0x9a, pass_ Through

0x1E, 0x01, port0

Address 0x07, 0x58, 948

0x08, 0x5c, port0 948 address alias

0x1E, 0x02, port1

Address 0x07, 0x58, 948

0x08, 0x5e, port1 948 address alias

After attempting to configure as above, only 948 (0x2E) on port0 can be accessed, while 948 on port1 cannot be detected

May I ask if there is any issue with the above configuration? How can I debug the 948 on port1 that cannot be detected?