Hi,

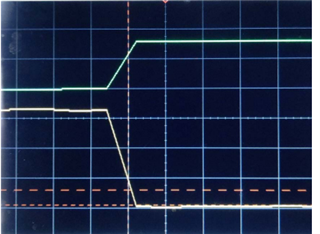

Here is Reset and COL signal waveform captured by my customer.

(Green:Reset(2V/div) Yellow:COL(1V/div) 10us/div)

It seems both signals changed simultaneously, but customer said COL line is not controlled by connected SoC.

(means, SoC pin that connected to COL pin of DP83822 is input)

If it's correct, it means that DP83822 drive COL pin low?

I feel a little weird that it seems COL start turning to low before Reset signal reached to its threshold.

And it would be very appreciated if you could capture reset and COL waveform of EVM for reference.

Thanks,

Go