Hi team,

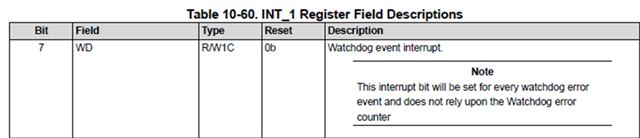

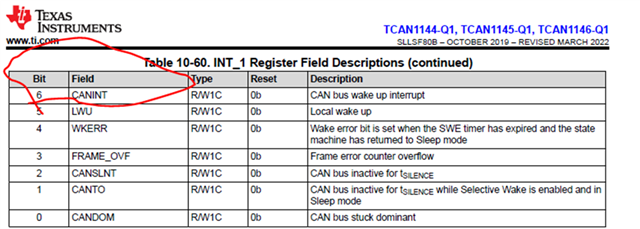

Customer is using CANoe to send CAN NM message every 40ms, and read CANINT bit through SPI every 5ms, they found the bit is never set. So they have below questions:

1. Will CANINT bit set any time (no matter STANBY or NORMAL state) when receiving CAN NM message?

2. If receive the command to clear CANINT bit, how long will it take? How long CANINT can be re-assert?

3. Is there any interval requirement of SPI read/write INT_1 register?

Thank you

Scarlett