Part Number: SN65DPHY440SS

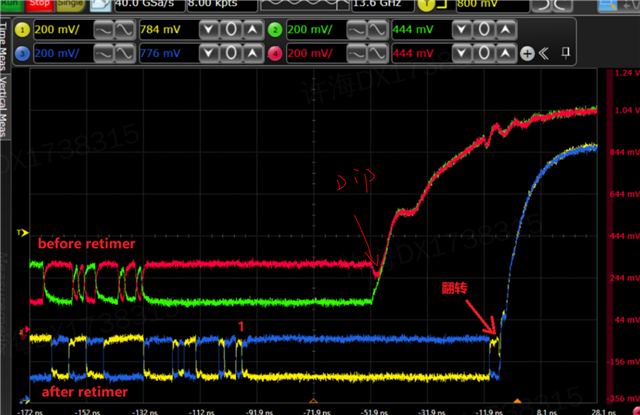

When we use the retimer to drive camera MIPI signal, the DB output will have peak as the capture shows:but when camera sensor connect to SOC directly, it does not have .

When the HS exit to LP,the THS-skip window has a bit flip.

Are they caused by the IC design bug or the design principle ?