Other Parts Discussed in Thread: SN65MLVD206, SN65MLVD204A

Hi, i am developing a half-duplex multipoint network based on M-LVDS. For now i am using just 2 nodes on the network, with a 30cm Cat5e cable, 100Ohms termination on both ends. The boards were hand prototyped so the tracks are not impedance matched.. but the max data rate i am using is 50Mbps and the max track lenght is about 2cm. The communication signal is being genarated by FPGAs on both side. I am driving DE ande RE pins with a single signal at both ends. The M-LVDS tranceivers are SN65MLVD206 and SN65MLVD204 (both type-2).

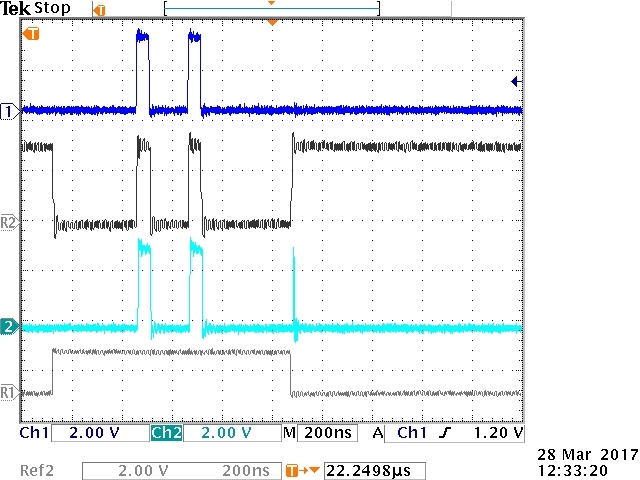

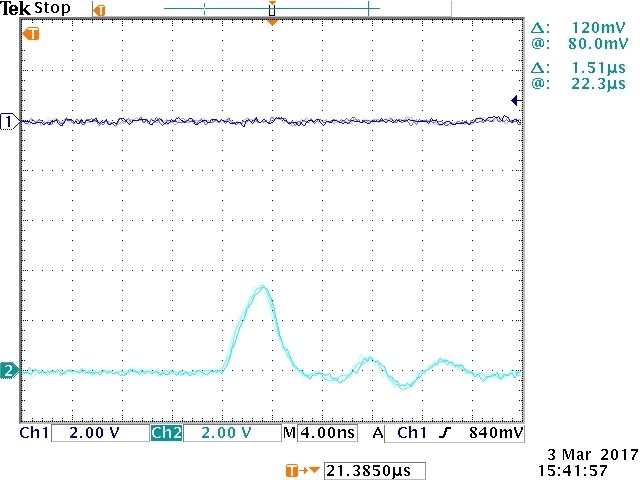

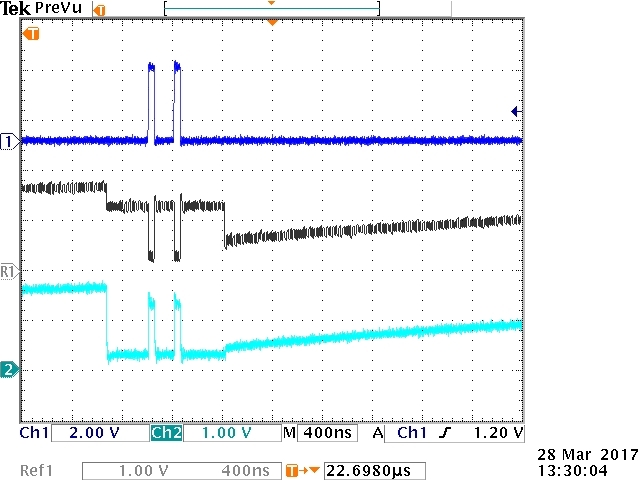

My problem is the following. When i put the DE/RE signal from high to low level a small pulse is generated on the receivers line. During this time, the differential line is floating, but i belive that is not the reason due to the type 2 failsafe and the line stays floating longer than the pulse. The LVTT lines are not Pulled Up or Down and the signal is alwyas on low logic level before disasserting DE/RE. Any ideal of the reason of this noise? Would leave the RE always on GND (Receiver active) solve this problem? If yes.. that is workable as i can just ignore any signal on the receivers line on the FPGA.

This pulse looks almost the same on every transition, so is not a noise source..

PS: To look at the signals i am using a 1Ghz scope, but as my probes are not well trimmed, the differential signal is very noise when i subtract both lines...

Thank you!