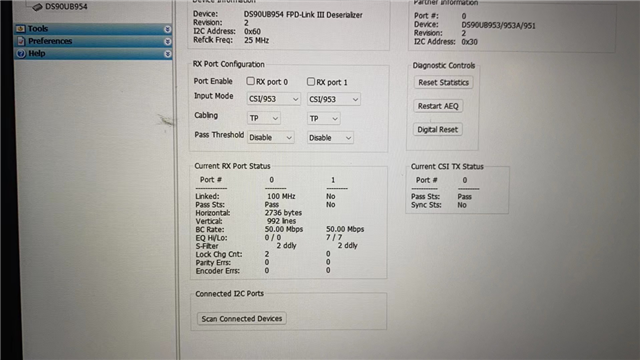

Part Number: DS90UB954-Q1

Hi Team,

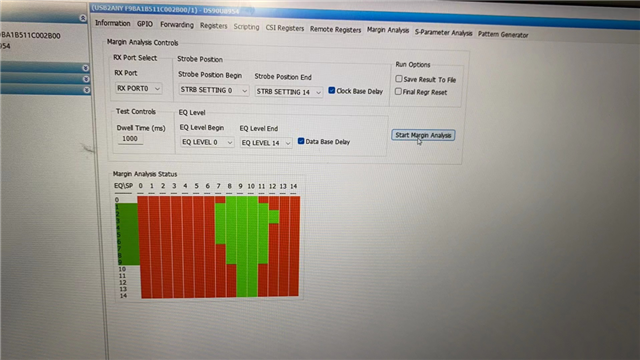

Customer use MAP tool to verify the link signal integrity and result showed below. There are two questions below:

- They test serval times and only first time failed, others are pass. Does this influence? Is there possibility the MAP tool bug cause first fail?

- Does MAP tool pass mean signal chain integrity are OK to use? If customer still found image error, any more methods or register need to be checked to debug?

Thank you!

Marc

Marc