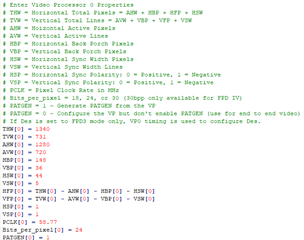

Hello, does the 947 support the second clock for LVDS (usually pinned between D6+ and D7-) ? And if not, will displays with dual LVDS channels continue to work?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.