HI

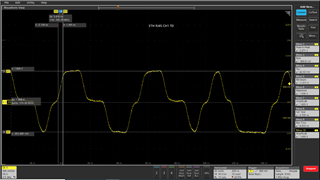

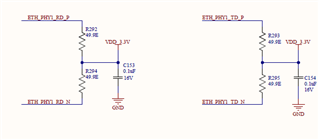

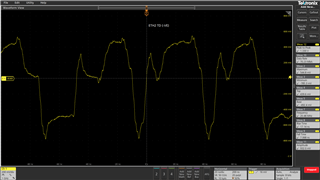

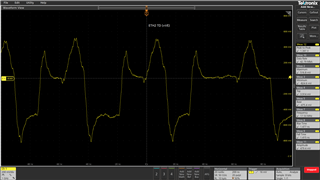

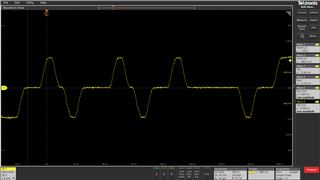

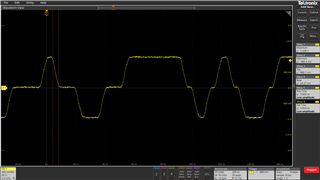

We are using DP83620SQE in our design along with AM625x. We are doing DVT analysis of our board and found the captures of the PMD output pair slightly exceeding 1.05V(max value as per datasheet). Please refer waveform below. It is 1.058V. We are using differential probe to validate these signals. Please let us know how much overshoot is allowable for these signals.