Part Number: DS90UB941AS-Q1

Other Parts Discussed in Thread: SN65DSI83

Hi Team,

Based on the internal image generator, the screen can be lit. A simplified application diagram is as follows:

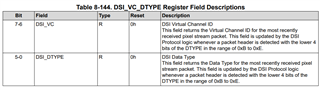

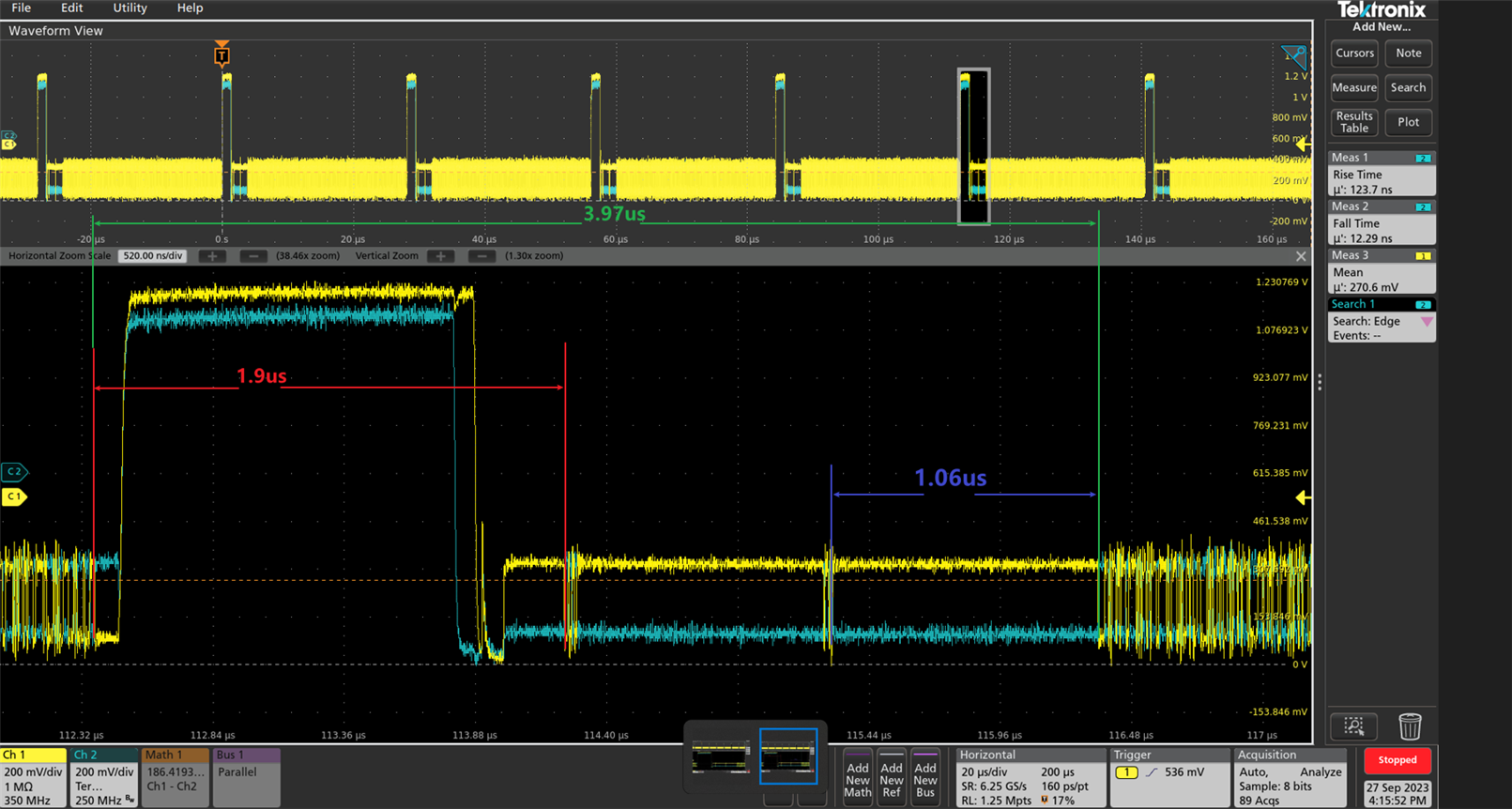

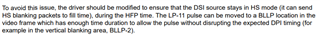

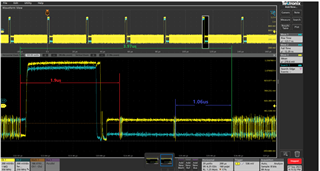

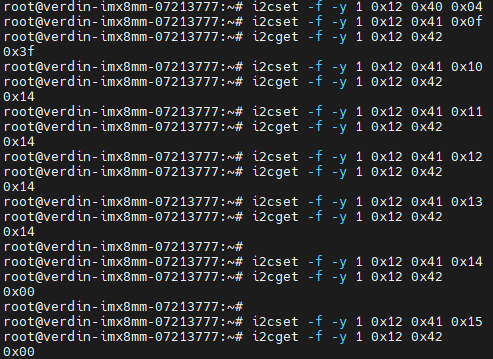

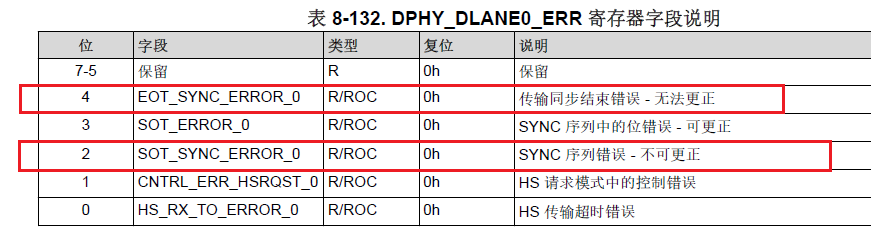

However, multiple attempts were made using the SoC's DSI data and clock and the screen still does not turn on. The DSI output is configured for video mode, burst mode, continuous clock mode. Through oscilloscope, it can be seen that the DSI can output normally. However, after the register configuration is performed, the screen still does not work. Checked DPHY related registers 0xF,0x10,0x11,0x12,0x13,0x14,0x15, status register values of all four data lane are 0x14 = 0001 0100, where bit2 and bit4 are indicated with errors:

The register configuration is as follows:

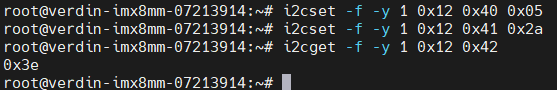

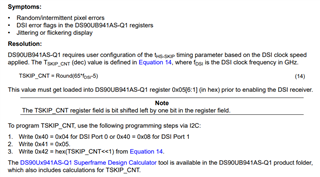

#!/bin/bash # 800x480p60, Dual Link FPD III # PCLK = 33.264MHz # DSI clock = 99.792MHz # DSI Lane Speed = 199.584Mbps/lane # 4 Lanes DSI # DSI input port 0 # DSI clock and DSI data # use i2c-tools to debug set -e I2C_BUS_NUMBER=1 UB941AS_ADDR=0x12 UB928_ADDR=0x2c # Disable DSI i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x01 0x08 # Select FPD-Link III Port 0 i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x1e 0x01 # Enable I2C_PASSTHROUGH i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x03 0x9a # Force select port 0 i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x5b 0x21 # Select DSI Port 0 digital registers i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x40 0x04 # Select DSI_CONFIG_0 register i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x41 0x20 # Set DSI_SYNC_PULSES = 0 i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x42 0x6f # Select DSI_CONFIG_1 register i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x41 0x21 # Set DSI_VS_POLARITY=DSI_HS_POLARITY=1 i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x42 0x60 #i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x42 0x00 # Set DSI_CONTINUOUS_CLOCK, single DSI, 4 lanes, DSI Port 0 input i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x4f 0x8c # DSI_HSW_CFG_HI i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x41 0x30 i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x42 0x00 # DSI_HSW_CFG_LO hsync-len = 48 i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x41 0x31 i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x42 0x30 # DSI_VSW_CFG_HI i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x41 0x32 i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x42 0x00 # DSI_VSW_CFG_LO vsync-len = 1 i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x41 0x33 i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x42 0x01 # TSKIP_CNT set DSI/D-PHY port0 i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x40 0x04 # TSKIP_CNT set indirect addr (reg DPHY_SKIP_TIMING) i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x41 0x05 # TSKIP_CNT set reg DPHY_SKIP_TIMING value i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x42 0x04 # Initialize DSI clock settings (From Section 10.2 of datasheet) i2cset -y -f $I2C_BUS_NUMBER $UB941AS_ADDR 0x40 0x10 i2cset -y -f $I2C_BUS_NUMBER $UB941AS_ADDR 0x41 0x86 i2cset -y -f $I2C_BUS_NUMBER $UB941AS_ADDR 0x42 0x0A i2cset -y -f $I2C_BUS_NUMBER $UB941AS_ADDR 0x41 0x94 i2cset -y -f $I2C_BUS_NUMBER $UB941AS_ADDR 0x42 0x0A # Enable DSI i2cset -y -f -r $I2C_BUS_NUMBER $UB941AS_ADDR 0x01 0x00

1) Dose this error indicating the SoC's DSI output is not configured correctly? Or what else error?

2) Customer only configured 941 registers, is 928 deserializer also required additional configuration?

Could you please help check this case? Thanks.

Best Regards,

Cherry