Other Parts Discussed in Thread: TLK1501

Hi there!

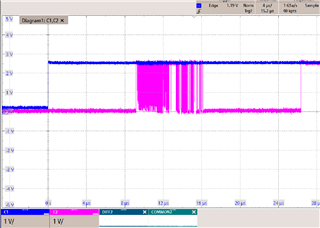

When I perform a BIST and enable the LOOPEN and PRBSEN functions at the same time, the RKLSB pin returns many PRBS error pulses.

Please, find attached the waveform here below:

LOOPEN (blue) / RKLSB (pink)

Otherwise, if PRBSEN is activated and then LOOPEN , the RKLSB pin doesn`t indicate any invalid PRBS sequence.

LOOPEN (blue) / RKLSB (pink)

Could you, please, confirm if this is a normal behavior for the TLK2711-SP?

Thank you in advance!

Regards,