Hi Ti experts,

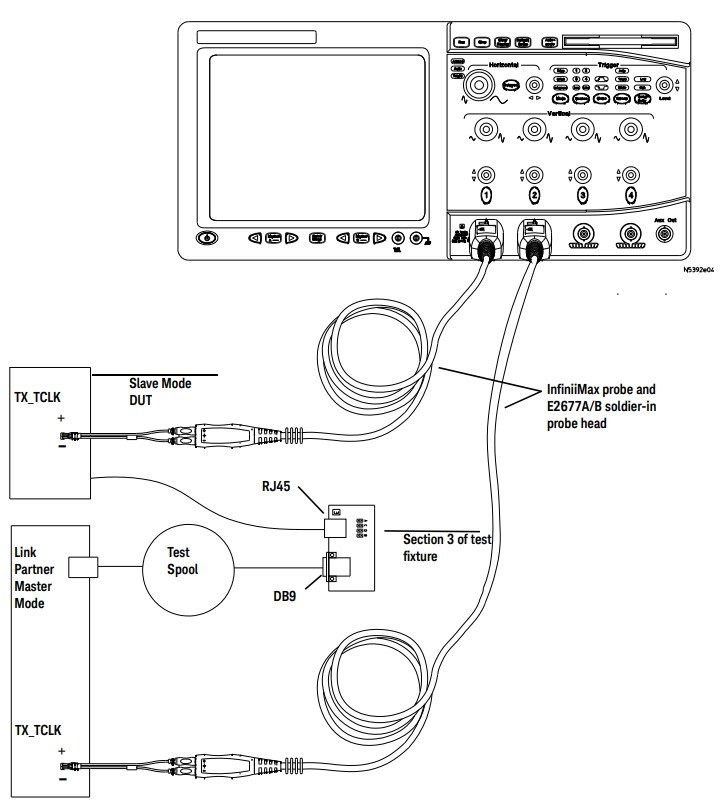

DP83867 compliance test, for probing for 1000 Base-T SLAVE TX_TCLK Jitter(Filtered and Unfiltered)

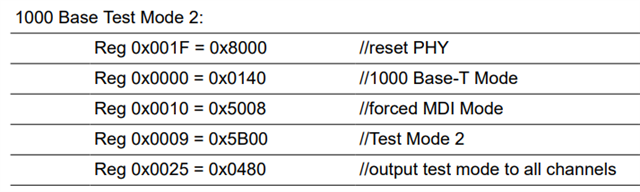

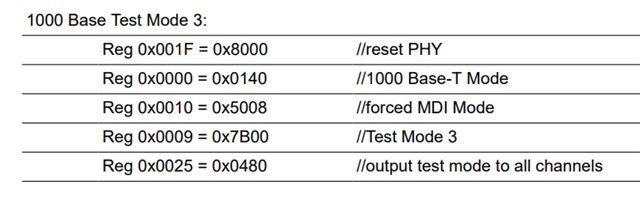

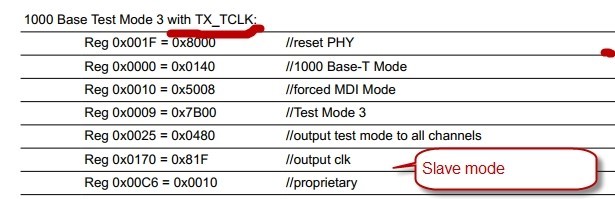

While DUT is operating in the SLAVE timing mode, the jitter on the DUT’s transmit clock (TX_TCLK) relative to the transmit clock (TX_TCLK) of a Link-Partner operating in the MASTER timing mode is less than 1.4 ns. So two TCLK is need, how to configure the DP83867 to generate two TCLK.

I have tried to put Master to work at test mode 2, and slave to work at test mode 3. But the two TCLK is not synchronous, so it fails to do the test.

What I need is the two TCLK is syncchronous.

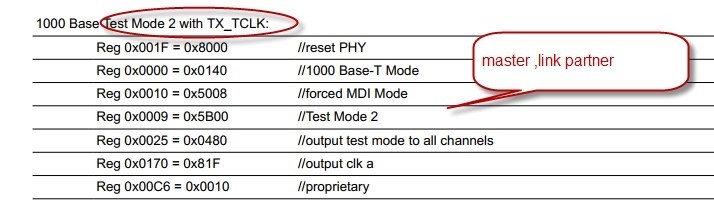

I have try that

So how to do the DP83867 compliance test for Slave jitter test with TCLK

Thanks