Other Parts Discussed in Thread: TUSB522P

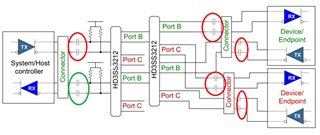

I have two HD3SS3212 are daisy chained and isolated from the surroundings using bypass capacitors on both RX and TX high speed lanes.

The two are biased to GND on the A0 and A1 ports.

The design is a USB3 5Gbit/s switch.

Is it necessary to isolate them using bypass capacitors in between and new bias resistors to maintain signal integrity?

We have problems with signal quality even though we have done the layout correctly (as we know it) and use a high quality pre-preg for high speed.