Hi TI engineers,

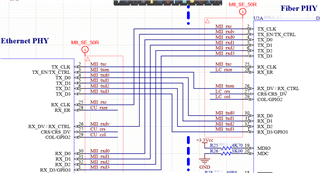

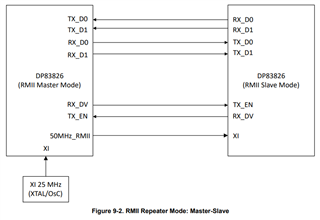

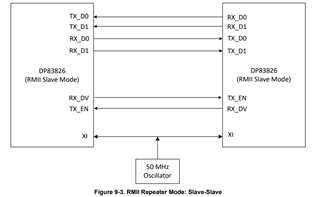

We have an ethernet card design that uses 2x DP83822IF configured in MII to accomplish MDI copper to MDI Fiber media conversion from a PCIe MAC.

The MAC and system processor do not have access to MDIO registers, so configuration of both DP83822 PHYs is done purely through HW bootstraps.

I have achieved successful, repetitive link-up @ 100Mbps and wanted to validate the stability of the MII link by doing an infinite ping test and monitor the packet loss.

Everytime, i get around 2-3% packet loss (out of thousands, sometimes thens of thousands of pings).

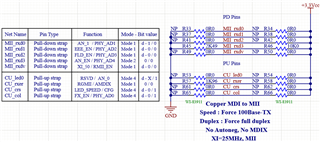

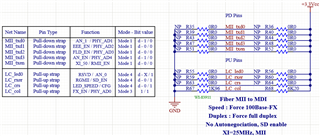

Our configuration is as follows :

Copper PHY

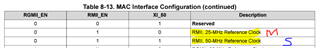

100Base-TX full-duplex, no MDIX, no autonogetiation, MII 25MHz, SD disabled

Fiber PHY

100Base-FX full duplex, no MDIX, no autonogetiation, MII 25MHz, FX enabled, SD enabled

Copper PHY <-> Fiber PHY MII Media converter connectivity:

TXD[0..3] -> RXD[0..3]

RXD[0..3] <- TXD[0..3]

TX_CLK -> RX_CLK

RX_CLK <- TX_CLK

TX_EN -> RX_DV

RX_DV <- TX_EN

RX_ER, CRS and COL are not shared connections between both PHYs.

The 25MHz clock between both PHY is shared, I.E one cmos oscillator that feeds both PHY. It is in spec with the minimum requirements for the DP83822IF (25MHz, ±25PPM).

Our strapping for both PHY is as follows, and as said previously, this works fine, we have a consistent link-up and disconnect through signal detect, and the network adapter in windows follows the state of SD.

My question is, do you have any clue as to why I might be getting a steady 2-3% packet loss?

I have a 2nd design that uses the same PCIe MAC to MDI copper, and 0% packet loss out of 100k+ pings. I am pretty sure that packet loss is due to media converter.

Thank you and fully available to provide more information on this subject!